Recommended

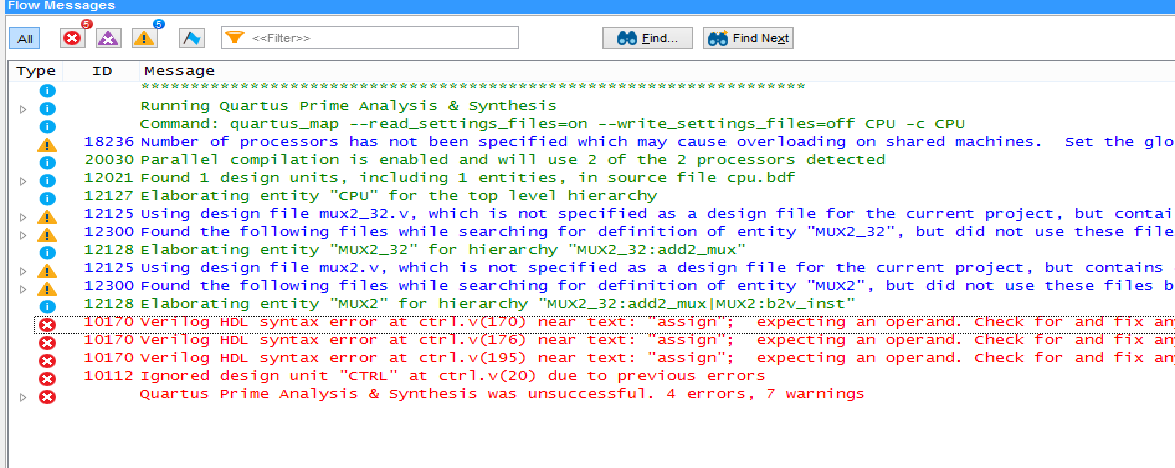

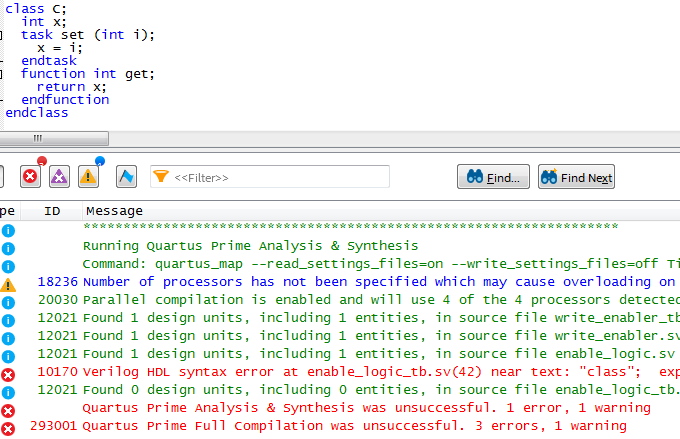

You may encounter an error indicating syntax error 10170 verilog hdl. It turns out that there are several ways to solve this problem, and this is what we will now look at. / Error (10170): Verilog HDL syntax error in .v (line_number) next to text message “,”; expects an operand. Due to your issue with Quartus® II software type 13.1 and above, you may receive the following error when compiling a Verilog HDL file converted from a block design file (.bdf).

Due to the situation in Quartus® II software version 13.1 and shortly thereafter, you may receive the following error message when Verilog compiles an HDL file converted from an HDL file: block construction (.bdf).

The reason for the error is that the entire generated Verilog HDL file contains almost all the extra commas in mov connections.

The reason for your syntax error can be described in such a way that you cannot simply write:

Product [7: 4] matches 4'b0000;

assign product [7: 4] is 4'b0000;

But if you are not using System Verilog (and your old-fashioned coding style might suggest that you are not), you will find that

product assignment [7: 4] includes 4'b0000;

also doesn’t compile, because the sad victim of the assign statement should automatically be wire , not reg . And if you replace product with a new stream , you will find yourself getting instructions and errors like this:

product means product >> 1; // move well and set the high bit to 0Product [7: 3] = product denion [7: 3] + multiplicable [4: 0]; // add 5 bits, so we'll probably deal with carry

product = fabric >> 1; // move all the way to the right

because you cannot assign a full stream in a always (or initial ) block.

You are starting to design a “shift and add art” multiplier and you probably really want to initialize the product at the beginning of the calculation. (Assuming you are creating syntax) lines

(assign) [7: 4] item = 4'b0000;(Assignment) the product [3: 0] is equal to the multiplier [3: 0];

run product constantly, every time; they do not initialize product . This is where you design hardware, not software.

Recommended

Is your PC running slow? Do you have problems starting up Windows? Don't despair! Fortect is the solution for you. This powerful and easy-to-use tool will diagnose and repair your PC, increasing system performance, optimizing memory, and improving security in the process. So don't wait - download Fortect today!

1234th56th7th8thnineteneleven12th13th14thfifteen1617th18th19th20th21 years22nd232425262728 year2930th31 year32333435 year363738394041 years4243 years old44 years45464748495051525354555657 years old5859

module kj (j1, l1, j, k, clock, reset, q, qb, q1, qb1, b);Input j1, l1, j, k, clock, reset;Output reg q1, qb1;Reg exit. [3: 0] q, qb, b, a;always @ (negative hours)beginCase (reset, j1, l1)3'b100: q1 = q1;3'b101: q1 = 0;3'b110: q1 = 1;3'b111: q1 = ~ q1;Default : q1 = 0;Back coverqb1 <= ~ q1;endalways@ *beginif (q1 == q1)beginkl JK1 (j, k, hours, reset, q [0], qb [0]);kl JK2 (j, k, q [0], reset, q [1], qb [1]);kl JK3 (j, k, q [1], reset, q [2], qb [2]);kl JK4 (j, k, q [2], reset, q [3], qb [3]);endendotherwise, if (q1 == 0)beginkl JK5 (j, k, d, reset, q [0], qb [0]);kl JK6 (j, k, q [0], reset, q [1], qb [1]);kl JK7 (j, k, q [1], reset, q [2], qb [2]);kl JK8 (j, k, q [2], reset, q [3], qb [3]);endAotherwise, if (q1 == 1)beginalways @ (reset)beginif (reset)q <= 4'b0000;otherwise, if (q <4'b0101)d <= d + 1;anotherb = q [1] && q [3];endendAotherwise, if (q1 == ~ q1)beginalways @ (clock setting)beginif (reset)q <= 4'b0000;otherwise, if (q <4'b0011)qQ + 1;AnotherA = q [2] & q [3];endendFinal module

<=

Why Do I Need To Fill In The CAPTCHA?

Completing this CAPTCHA proves that you are human and gives you temporary access to a web resource.

What Can I Do To Prevent This From Happening In The Future?

If you are more likely to have face-to-face communication, such as visiting your home, you can run a scancheck for viruses on your device to make sure it is not infected with malware.

If you are in the office or on a shared network, you can find a network administrator who will run a custom network scan to support misconfigured or infected devices.

Another way to reduce access to this page in the enhanced version is to use Passport Privacy. You may now need to download version 2.0 from the Firefox Add-on Store.

Error 10170 Compilation format error

I am the latest in Verilog. System error of the if statement.

Can a person help me by rejecting my mistake?

This is partially related code I wrote. The following

error occurs

Error (10170): Verilog HDL syntax error in seqdet.v (24) next to if content;

Waiting for an identifier ("if" is a reserved keyword), quantity, system or

backchi, or "(" and also "{" or unary operator,

current_state is in register type, and reset_state was initialized to 3'b000 using the

parameter instruction.

Post by Jughead

I'm new to Verilog. Collect error for if statement.

Can the player help me by pointing out my mistake ?. [2: 0]

reg next_state, current_state;

the reset_state parameter means 3'b000;

case (data)

{

if (current_state == reset_state)

begin

next_state means reset_state;

end

This is part because of the code I wrote. There is the following error

Verilog error (10170): HDL syntax error in seqdet.v (24) next to the anchor text "if";

Waiting for an identifier ("if" is a keyword of any type of reserved identifier), or #, or

of a system task, or "(", with "{", or a unary operator,

current_state is associated with a type register, and reset_state is initialized to 3 'b000 with parameter declaration. Out

thanks,

aravind

This case statement did not have large opening and closing

statements, and it was enclosed in curly braces, which, in my opinion, was unnecessary. Not sure if I'm right. But now I am notI understand all our mistakes.

used for bitstring. Use start-end instead.

Don't forget the "endcase".

used for both bitstring. Use start-end instead. Film Not such an "extreme case".

Speed up your PC today with this easy-to-use download.

Fehler 10170 Verilog Hdl Syntaxfehler

Fout 10170 Verilog Hdl Syntaxisfout

오류 10170 Verilog Hdl 구문 오류

Erro 10170 Erro De Sintaxe Hdl Verilog

Erreur 10170 Erreur De Syntaxe Verilog Hdl

Fel 10170 Verilog Hdl Syntaxfel

Errore 10170 Errore Di Sintassi Verilog Hdl

Blad 10170 Verilog Blad Skladni Hdl

Oshibka 10170 Sintaksicheskaya Oshibka Verilog Hdl

Error 10170 Error De Sintaxis De Verilog Hdl