Rekommenderas

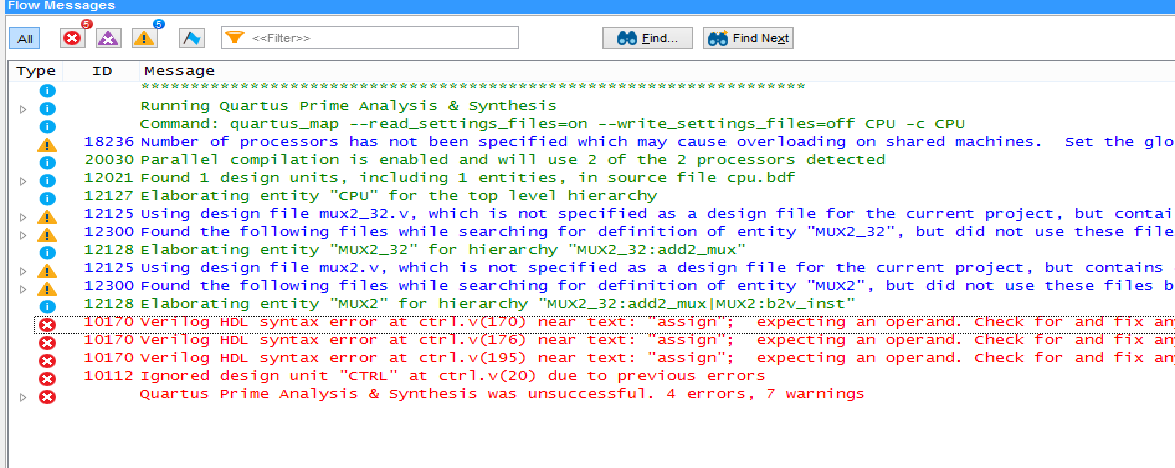

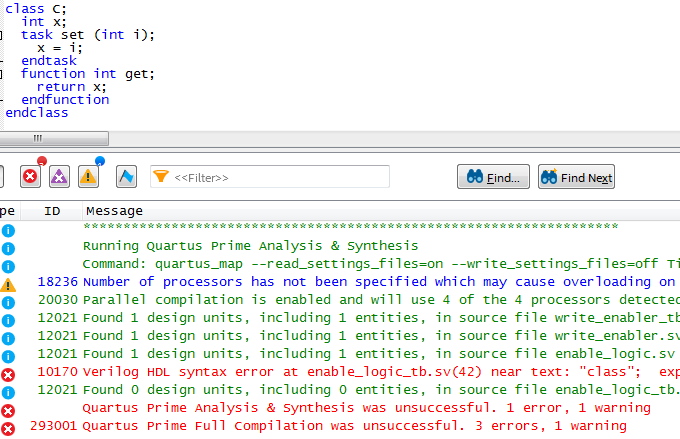

Du kan mycket väl stöta på ett fel som anger syntaxfel i bedömning 10170 verilog hdl. Det visar sig att det finns flera sätt att lösa detta problem, och det här rådet är vad vi nu kommer att titta på./ Fel (10170): Verilog HDL -syntaxfel i ./ (radnummer) bredvid textmeddelande “,”; förväntar sig bra operand. På grund av ditt problem med Quartus® II -programvarutyp 13.1 och senare kan du få följande fel när du sammanställer en Verilog HDL -fil som konverterats från en blockdesigndata (.bdf).

På grund av situationen i Quartus® II -produkter version 13.1 och kort därefter kan du få följande felmeddelande när Verilog sammanställer utmärkt HDL -fil konverterad från en HDL -fil: hindra konstruktion (.bdf).

Orsaken till typen av fel är att hela den genererade Verilog HDL -arkiveringen innehåller nästan alla extra kommatecken i transportförbindelser.

Orsaken till ditt formatfel kan beskrivas på ett sådant sätt att du inte bara kan skriva:

Produkt [7: 4] matchar 4'b0000;

tilldela varor [7: 4] är 4'b0000;

Men om du upptäcker att du inte använder System Verilog (och din gammaldags programmeringsstil kan föreslå att du inte är det) kommer du att upptäcka det

produktutmaning [7: 4] inkluderar 4'b0000;

kompileras inte heller, när det sorgliga offret för bestämma -uttalandet automatiskt ska vara tråd , inte på något sätt reg . Och om du byter produkt med en ny tillhandahåller , får du instruktioner och nackdelar så här:

produkt betyder modell >> 1; // flytta väl och ställ den övre biten till 0Produkt [7: 3] = svarsförnekelse [7: 3] + multiplikerbar [4: 0]; // kombinera 5 bitar, så vi kommer förmodligen att handla med bär

product = tyg >> 1; // fortsätt att flytta hela vägen till höger

eftersom de inte kan tilldela en fullständig ström som en del av en alltid (eller för att starta med ) block.

Du börjar designa en “skift och lägg till konst” -multiplikator och du vill utan tvekan verkligen initiera tillägget i början av beräkningen. (Antar att du har skapar syntax) rader

(tilldela) [7: 4] item = 4'b0000;(Uppgift) produkten [3: 0] är ofta lika med multiplikatorn [3: 0];

genomföra produkt konstant, varje gång; detta företag initierar inte produkt . Det är vanligtvis där du designar hårdvara, inte programvara.

Rekommenderas

Körs din dator långsamt? Har du problem med att starta Windows? Misströsta inte! Fortect är lösningen för dig. Detta kraftfulla och lättanvända verktyg kommer att diagnostisera och reparera din dator, öka systemets prestanda, optimera minnet och förbättra säkerheten i processen. Så vänta inte - ladda ner Fortect idag!

1234: e56: e7: e8: eniotioelva12: e13: e14: efemton1617: e18: e19: e20: e21 år22: a232425262728 år2930: e31 år32333435 år363738394041 år4243 år gammal44 år45464748495051525354555657 ett antal gamla5859

modul kj (j1, l1, j, e, clock, reset, q, qb, q1, qb1, b);Ingång j1, l1, j, k, klocka, återställning;Utmatningsreg q1, qb1;Reg exit. [3: 0] q, qb, b, a;alltid vid (negativa timmar)BörjaFodral (återställ, j1, l1)3'b100: q1 innebär q1;3'b101: q1 = 0;3'b110: q1 = 1;3'b111: q1 betyder ~ q1;Standard: q1 = 0;Bakstycketqb1 <=! q1;slutetalltid@ *Börjaom (q1 == q1)Börjakl JK1 (j, k, timmar, återställning, q [0], qb [0]);kl JK2 (j, k, q [0], reset, q [1], quarterback [1]);kl JK3 (j, k, q [1], reset, w [2], qb [2]);kl JK4 (j, k, t [2], reset, q [3], qb [3]);slutetslutetannars, om (q1 == 0)Börjakl JK5 (j, k, d, reset, n [0], qb [0]);kl JK6 (j, k, q [0], helt återställd, q [1], qb [1]);kl JK7 (j, k, t [1], reset, q [2], qb [2]);kl JK8 (j, k, q [2], reset, q [3], quarterback [3]);slutetAannars, om (q1 == 1)Börjaalltid @ (återställ)Börjaom (återställ)q <= 4'b0000;annars, om (q <4'b0101)d <= d + 1;annanb innebär q [1] && q [3];slutetslutetAannars, när som helst (q1 == ~ q1)Börjaalltid @ (klockinställning)Börjaom (återställ)q <= 4'b0000;annars, om (q <4'b0011)qQ + 1;AnnanA = t [2] & q [3];slutetslutetSlutmodul

<=

Varför behöver jag fylla i CAPTCHA?

Att slutföra denna CAPTCHA är att du är människa och ger dig kortsiktig tillgång till en webbresurs.

Vad kan jag göra för att förhindra att detta händer i framtiden?

Om det är mer troligt att du har kommunikation ansikte mot ansikte nu, till exempel att besöka ditt hem, kan ägare köra en granskning av virus på din egen enhet för att se till att den inte är skadad med skadlig kod.

Om du är på kontoret eller i ett stort delat nätverk kan du hitta en nätverksägare som kommer att köra en anpassad nätverksskanning för att stödja felkonfigurerade eller infekterade enheter.

Ett annat bra sätt att minska åtkomsten till denna sida i en viss förbättrad version är att använda Passport Privacy. Du kan nu behöva ladda ner version 2.0, till exempel Firefox Add-on Store.

Fel 10170 Fel vid kompileringsformat

Jag är den toppmoderna i Verilog. Systemfel i if -historiken.

Kan en person hjälpa mig att avvisa mitt misstag?

Detta är delvis relaterad kupong som jag skrev. Följande

fel är associerat

Fel (10170): Verilog HDL -syntaxfel på seqdet.v (24) bredvid if content;

Väntar bara på en identifierare ("om" är ett reserverat nyckelord), överflöd, system eller

backchi, eller "(" och och "{" eller unary operator,

current_state visas i registertyp och reset_state initialiserades i 3'b000 med hjälp av parameterinstruktionen

.

Inlägg skrivet av Jughead

Jag är ny på Verilog. Samla fel för if -satsen.

Kan spelaren hjälpa mig genom att påpeka mitt misstag?. [2: 0]

reg next_state, current_state;

dess parameter reset_state betyder 3'b000;

fall (data)

{

om kanske (current_state == reset_state)

börja

next_state betyder reset_state;

slutet

Detta är en del på grund av koden jag skrev. Det finns följande fel

Verilog -fel (10170): HDL -syntaxfel i seqdet.v (24) för det andra till ankartexten "if";

Väntar på en identifierare ("om" är ett nyckelord som är länkat till någon typ av reserverad identifierare), eller #, tillsammans med

av en systemuppgift, eller "(", som innehåller "{", eller en unary operatör ,

current_state är vanligtvis associerat med ett typregister, och reset_state kan initieras till 3 'b000 med parameterdeklaration. Ut

tack, aravind

Det här evenemangsuttalandet hade inte stora öppnings- och avslutande

uttalanden, och det var inneslutet i fula hängslen, vilket enligt min mening var onödigt. Vet inte om jag har rätt. Men nu känner jag inte att jag förstår alla våra misstag.

används för bitsträngar. Använd start-end istället.

Glöm inte en persons "endcase".

används för båda bitsträngarna. Använd start-end istället. Film Inte så "extrema fall".

Få fart på din dator idag med denna lättanvända nedladdning.Error 10170 Verilog Hdl Syntax Error

Fehler 10170 Verilog Hdl Syntaxfehler

Fout 10170 Verilog Hdl Syntaxisfout

오류 10170 Verilog Hdl 구문 오류

Erro 10170 Erro De Sintaxe Hdl Verilog

Erreur 10170 Erreur De Syntaxe Verilog Hdl

Errore 10170 Errore Di Sintassi Verilog Hdl

Blad 10170 Verilog Blad Skladni Hdl

Oshibka 10170 Sintaksicheskaya Oshibka Verilog Hdl

Error 10170 Error De Sintaxis De Verilog Hdl