Recommandé

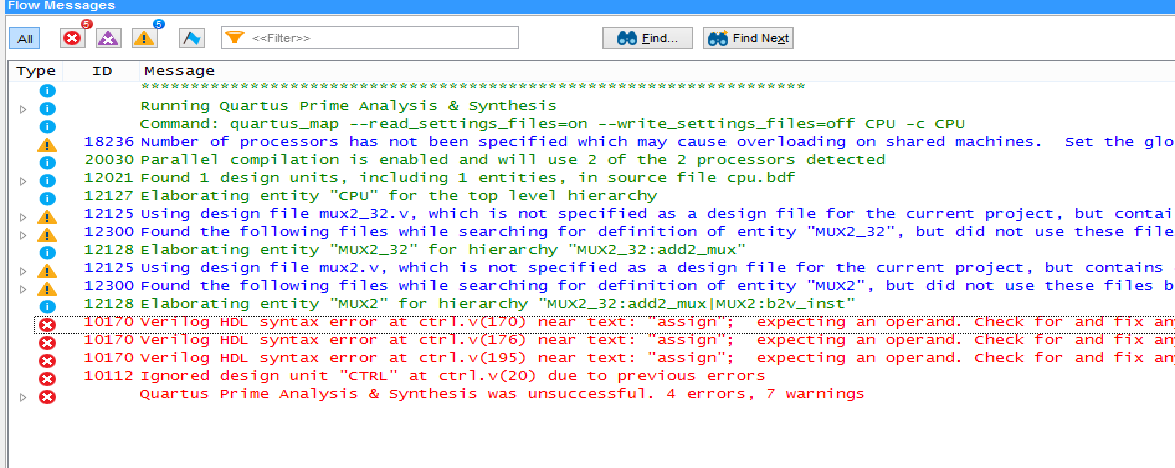

Vous rencontrez probablement une erreur indiquant des erreurs de syntaxe 10170 verilog hdl. Il s’avère qu’il existe plusieurs façons de résoudre ce problème, et c’est celle-ci que nous allons maintenant examiner./ Erreur (10170): Erreur de syntaxe Verilog HDL dans .w (numéro_ligne) à côté du message texte “,”; attend un nouvel opérande. En raison de votre problème avec le logiciel Quartus® II de type 13.1 et supérieur, l’erreur suivante peut vous être attribuée lors de la compilation d’un fichier Verilog HDL converti à partir d’un fichier de données de conception de bloc (.bdf).

En raison de la situation dans la version 13.1 du programme Quartus® II et peu de temps après, le message d’erreur suivant peut s’afficher lorsque Verilog compile un fichier HDL puissant converti à partir d’un fichier HDL : construction de blocage (.bdf).

La raison de cette erreur est que l’intégralité du registre Verilog HDL généré contient presque toutes les virgules supplémentaires dans les connexions de transfert.

La raison de votre erreur de format peut être décrite de telle manière que vous ne pouvez pas simplement écrire :

Le produit [7 : 4] correspond à 4'b0000 ;

assign design [7: 4] est 4'b0000 ;

Mais si vous n’utilisez vraiment pas System Verilog (et votre style de construction de site à l’ancienne peut suggérer que vous ne l’utilisez pas), votre organisation le découvrira

Le thème du produit

[7 : 4] inclut 4'b0000 ;

ne compile pas non plus, car la triste victime de l’instruction allow devrait être automatiquement wire , pas vraiment reg . Et si vous remplacez le produit par un nouveau fourniture , vous vous retrouverez avec des instructions et des échecs comme celui-ci :

produit signifie service >> 1 ; // bouge bien et met le bit le plus élevé à 0Produit [7 : 3] = articles denion [7 : 3] + multiplicable [4 : 0] ; // inclure 5 bits, nous aurons donc probablement une raison suffisante pour le report

produit = tissu >> 1 ; // transition complètement vers la droite

car les utilisateurs ne peuvent pas attribuer un flux complet par rapport à un toujours (ou fondamental < /code>).

Vous commencez à concevoir chaque multiplicateur "shift and add art" et vous voudrez peut-être vraiment initialiser le modèle au début du calcul. (En supposant que vos besoins créent une syntaxe) lignes

(attribuer) [7 : 4] élément = 4'b0000 ;(Affectation) le produit [3 : 0] a été égal au multiplicateur [3 : 0] ;

faire défiler le produit constamment, à chaque fois ; ces produits n'initialisent pas produit . C'est essentiellement là que vous concevez du matériel, pas du logiciel.

Recommandé

Votre PC est-il lent ? Avez-vous des problèmes pour démarrer Windows ? Ne désespérez pas ! Fortect est la solution pour vous. Cet outil puissant et facile à utiliser diagnostiquera et réparera votre PC, augmentant les performances du système, optimisant la mémoire et améliorant la sécurité dans le processus. Alors n'attendez pas - téléchargez Fortect dès aujourd'hui !

1234e56e7e8eneufDixOnze12e13e14equinze1617e18e19e20e21 ans22e232425262728 ans2930e31 ans32333435 ans363738394041 ans4243 ans44 ans45464748495051525354555657 cycles de croissance vieux5859

module kj (j1, l1, j, c, clock, reset, q, qb, q1, qb1, b);Entrée j1, l1, j, k, horloge, réinitialisation ;Sortie reg q1, qb1;Sortie Reg. [3 : 0] q, qb, b, a ;toujours à (heures négatives)commencerCas (réinitialisation, j1, l1)3'b100 : q1 implique q1 ;3'b101 : q1 = 0 ;3'b110 : q1 = 1 ;3'b111 : q1 implique ~ q1 ;Par défaut : q1 = 0 ;Quatrième de couvertureqb1 <= ! q1 ;finirtoujours@ *commencersi (q1 == q1)commencerkl JK1 (j, k, heures, remise à zéro, q [0], qb [0]);kl JK2 (j, k, q [0], remise à zéro, q [1], quarterback [1]);kl JK3 (j, k, q [1], réinitialiser, n [2], qb [2]);kl JK4 (j, k, k [2], réinitialiser, q [3], qb [3]);finirfinirsinon, si (q1 == 0)commencerkl JK5 (j, k, d, réinitialiser, w [0], qb [0]);kl JK6 (j, k, q [0], régler, q [1], qb [1]);kl JK7 (j, k, k [1], réinitialiser, q [2], qb [2]);kl JK8 (j, k, q [2], remise à zéro, q [3], quarterback [3]);finirUNEsinon, si (q1 == 1)commencertoujours @ (réinitialiser)commencersi (réinitialiser)q <= 4'b0000;sinon, si (q <4'b0101)d <= d + 1 ;un autreb est égal à q [1] && q [3];finirfinirUNEsinon, à condition que (q1 == ~ q1)commencertoujours @ (réglage de l'horloge)commencersi (réinitialiser)q <= 4'b0000;sinon, si (q <4'b0011)qQ + 1 ;Un autreA = b [2] & q [3] ;finirfinirModule final

<=

Pourquoi dois-je remplir le CAPTCHA ?

Remplir ce CAPTCHA s'avère que vous êtes un être humain et vous donne temporairement accès à une ressource Web.

Que puis-je faire pour éviter que cela ne se reproduise à l'avenir ?

Si vous êtes plus susceptible d'avoir une communication en face à face, comme une visite à votre domicile, la personne peut effectuer une recherche de virus sur cet appareil pour s'assurer qu'il n'est pas contaminé par des logiciels malveillants.

Si vous êtes au bureau ou sur un réseau partagé complet, vous pouvez trouver un administrateur réseau qui exécutera une analyse réseau personnalisée pour prendre en charge les appareils mal configurés ou infectés.

Une autre manière de réduire l'accès à cette page dans votre version améliorée est d'utiliser Passport Privacy. Vous devrez peut-être maintenant télécharger la version 2.0 en utilisant le Firefox Add-on Store.

Erreur 10170 Erreur de format de compilation

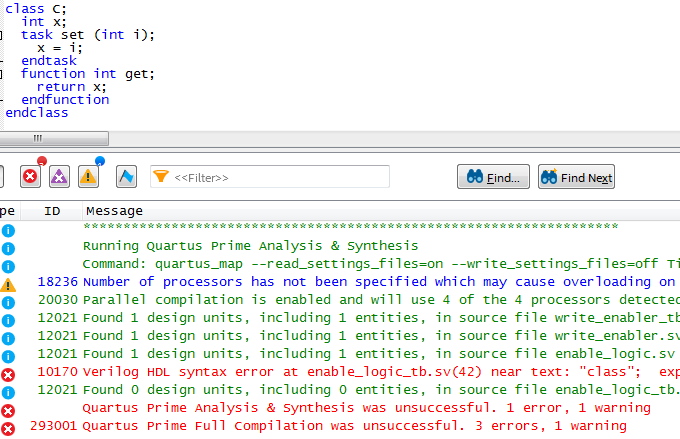

Je suis l'actuelle tendance de Verilog. Erreur système de la stratégie if.

Une personne peut-elle m'aider à rejeter mon erreur ?

Il s'agit d'un codage partiellement lié que j'ai écrit. L'erreur

suivante est présente

Erreur (10170) : erreur de syntaxe Verilog HDL dans seqdet.v (24) à côté de if content ;

Attente d'un identifiant ("if" est un mot-clé réservé), portion, système ou

backchi, ou "(" et bien trop "{" ou opérateur unaire,

current_state est à travers le type de registre, et reset_state a été initialisé pour aider 3'b000 à l'aide de l'instruction de paramètre

.

Message de Jughead

Je suis nouveau sur Verilog. Collecter l'erreur pour l'instruction if.

Le joueur peut-il me signaler mon erreur ?. [2 : 0]

reg next_state, current_state ;

le paramètre reset_state signifie 3'b000 ;

cas (données)

{

si cela s'avère (current_state == reset_state)

begin

next_state signifie reset_state ;

end

C'est en partie à cause du code que j'ai montré. Il y a l'erreur suivante

Erreur Verilog (10170) : erreur de syntaxe HDL dans seqdet.v (24) poursuivant vers le texte d'ancrage "if" ;

Attente d'un identifiant ("if" est un mot-clé à cause de tout type d'identifiant réservé), ou #, en revanche

d'une tâche système, ou "(", conjointement avec "{", ou un opérateur unaire,

current_state sont associés à un registre de type, et reset_state serait initialisé à 3 'b000 avec déclaration de paramètre. Out

merci,

aravind

Cette déclaration de problème n'avait pas de grandes déclarations d'ouverture et de règlement

, et elle était entourée d'accolades laides, ce qui, à mon avis, était inutile. Je ne sais pas si j'ai raison. Mais maintenant je n'étais pas, je comprends toutes nos erreurs.

utilisé nécessaire pour la chaîne de bits. Utilisez plutôt début-fin.

N'oubliez pas votre "endcase".

utilisé pour les deux chaînes de bits. Utilisez plutôt début-fin. Film Ce n'est pas un "cas extrême".

Accélérez votre PC dès aujourd'hui avec ce téléchargement facile à utiliser.

Error 10170 Verilog Hdl Syntax Error

Fehler 10170 Verilog Hdl Syntaxfehler

Fout 10170 Verilog Hdl Syntaxisfout

오류 10170 Verilog Hdl 구문 오류

Erro 10170 Erro De Sintaxe Hdl Verilog

Fel 10170 Verilog Hdl Syntaxfel

Errore 10170 Errore Di Sintassi Verilog Hdl

Blad 10170 Verilog Blad Skladni Hdl

Oshibka 10170 Sintaksicheskaya Oshibka Verilog Hdl

Error 10170 Error De Sintaxis De Verilog Hdl