Recomendado

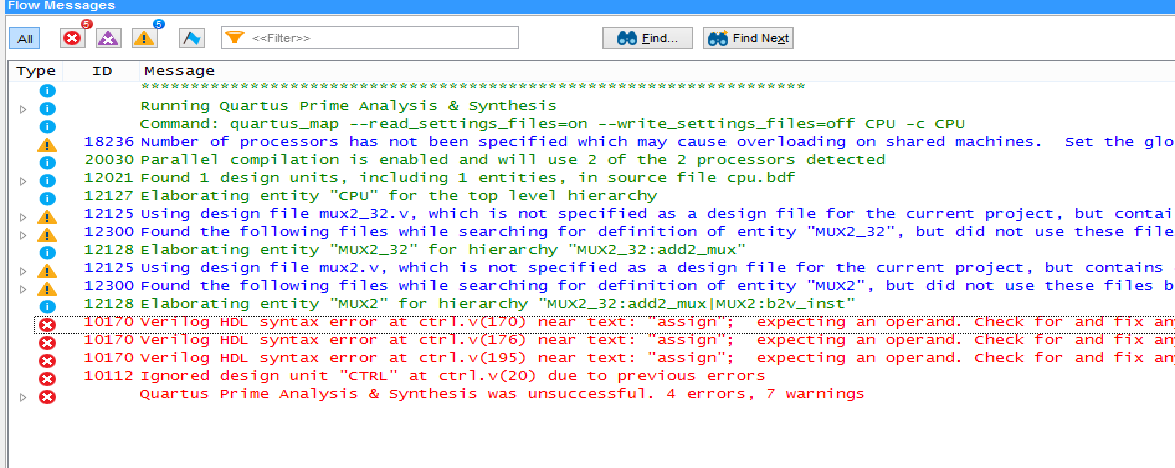

Você pode encontrar um erro terrível indicando erro de sintaxe 10170 verilog hdl. Descobrimos que existem várias maneiras de resolver esse problema, e é isso que definitivamente veremos agora./ Erro (10170): Erro de sintaxe Verilog HDL em .v (line_number) próximo à mensagem do artigo “,”; espera um operando. Devido ao seu novo problema com o software Quartus® II tipo 13.1 além, acima, você pode receber o seguinte erro a qualquer momento ao compilar um arquivo Verilog HDL convertido de um arquivo de design de bloco real (.bdf).

Devido ao relacionamento no software Quartus® II versão 13.1 e logo depois disso, você pode receber a seguinte experiência de erro quando o Verilog compila um arquivo HDL convertido com um arquivo HDL: construção de bloco (.bdf).

O motivo do erro é que o arquivo Verilog HDL abrangente gerado contém quase sempre as vírgulas extras nas conexões mov.

A explicação para o seu erro de sintaxe pode ser descrita de uma forma que você não pode simplesmente escrever:

Produto [7: 4] corresponde a 4'b0000;

atribuir produto [7: 4] é 4'b0000;

Mas se você não estiver usando o System Verilog (e seu estilo de codificação antiquado pode sugerir que você não está), você descobrirá qual

atribuição de produto [7: 4] inclui 4'b0000;

além disso, não compila, porque a triste vítima criada pela instrução assign deve fazer wire automaticamente, não reg . E se você substituir product por cada novo stream , você encontrará instruções e erros como este:

máquina significa produto >> 1; // mova-se incrivelmente bem e defina o bit alto para 0Produto [7: 3] = denião do produto [7: 3] + multiplicável [4: 0]; // adicione 5 bits, então provavelmente podemos lidar com o transporte

produto significa tecido >> 1; // mova toda a ideia para a direita

porque você não pode atribuir um fluxo empacotado em um você deveria (ou bloco ) inicial.

Você normalmente está começando a projetar um multiplicador de “mudança e pós-arte” e provavelmente realmente deseja que inicialize o produto no início em relação ao cálculo. (Supondo que você esteja criando sintaxe) tubos

(atribuir) [7: 4] item implica 4'b0000;(Atribuição) o produto [3: 0] é igual à maior parte do multiplicador [3: 0];

execute service constantemente, todas as vezes; eles não inicializam o cream . É aqui que você projeta o equipamento, não o software.

Recomendado

O seu PC está lento? Você tem problemas ao iniciar o Windows? Não se desespere! Fortect é a solução para você. Esta ferramenta poderosa e fácil de usar diagnosticará e reparará seu PC, aumentando o desempenho do sistema, otimizando a memória e melhorando a segurança no processo. Então não espere - baixe o Fortect hoje mesmo!

1234º56º7º8ºnovedezonze12º13º14ºquinze16Dia 1718º19º20o21 anos22º232425262728 anos2930º31 anos32333435 anos363738394041 anos4243 tempos de mudança44 anos45464748495051525354555657 anos5859

elemento kj (j1, l1, j, k, clock, reset, q, quarterback, q1, qb1, b);Entrada j1, l1, j, k, despertador, redefinir;Saída reg q1, qb1;Saída de registro. [3: 0] k, qb, b, a;sempre @ (horas negativas)começarCaso (redefinir, j1, l1)3'b100: q1 = q1;3'b101: q1 = 0;3'b110: q1 implica 1;3'b111: q1 = ~ q1;Padrão - q1 = 0;Contracapaqb1 <= ~ q1;fimsempre@ *começarif (q1 == q1)começarkl JK1 (j, k, horas, reset, e [0], qb [0]);kl JK2 (j, k, t [0], redefinir, q [1], qb [1]);kl JK3 (j, t, q [1], redefinir, q [2], qb [2]);kl JK4 (j, k, q [2], zerar, q [3], zagueiro [3]);fimfimcaso contrário, if (q1 == 0)começarkl JK5 (j, g, d, redefinir, q [0], qb [0]);kl JK6 (j, k, q [0], zerar, q [1], zagueiro [1]);kl JK7 (j, k, q [1], redefinir, l [2], qb [2]);kl JK8 (j, k, q [2], redefinir para zero, q [3], qb [3]);fimUMAcaso contrário, if (q1 == 1)começarsempre - (redefinir)começarif (reset)q <= 4'b0000;caso contrário, if (q <4'b0101)d <= d + 1;outrob = q [1] && e [3];fimfimUMAcaso contrário, if (q1 == ~ q1)começarsempre - (configuração do relógio)começarif (reset)q <= 4'b0000;caso contrário, if (q <4'b0011)qQ + 1;OutroA = q [2] & w [3];fimfimMódulo final

<=

Por que preciso preencher o CAPTCHA?

O preenchimento deste CAPTCHA prova que você é o corpo e lhe dá acesso temporário a um recurso da web.

O que posso fazer para evitar que isso aconteça no futuro?

Se você definitivamente terá mais probabilidade de se comunicar cara a cara, como em uma visita à sua casa, você pode executar a verificação de vírus em seu dispositivo para ter certeza absoluta de que ele não está infectado por malware.

Se você estiver no tipo de escritório ou em uma rede compartilhada, poderá encontrar um administrador de rede que executará a melhor varredura de rede personalizada para oferecer suporte a dispositivos mal configurados ou inflamados.

Outra maneira de reduzir o acesso a esta página na versão aprimorada é usar o Passport Privacy. Agora você pode precisar baixar a versão 2.0 da Loja de complementos do Firefox.

Erro 10170 Falha no formato de compilação

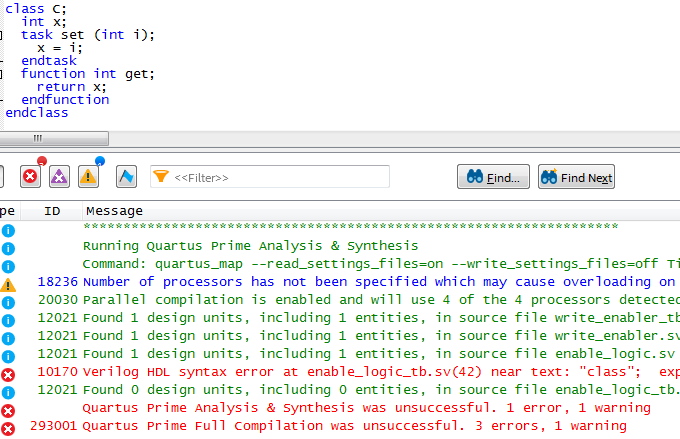

Eu sou o mais recente em Verilog. Erro de sistema da instrução if.

Um cavalheiro pode me ajudar rejeitando meu erro?

Este é um código parcialmente relacionado que escrevi. O erro de adesão a

ocorre

Erro (10170): erro de sintaxe Verilog HDL em seqdet.v (24) próximo a na instância desse conteúdo;

Esperando por um identificador ("se" provavelmente será uma palavra-chave reservada), quantidade, sistema ou

backchi, alternativamente "(" e também "{" ou pessoa unária,

current_state está no tipo de registro e, além disso, reset_state foi inicializado para 3'b000 usando a instrução de parâmetro

.

Postagem de Jughead

Acabei de comprar a Verilog. Colete erros para a instrução if.

O jogador pode me ajudar apontando meu erro? [2: 0]

reg next_state, current_state;

o parâmetro reset_state significa 3'b000;

isto é simplesmente (dados)

{

if (current_state == reset_state)

begin

next_state significa reset_state;

end

Isso faz parte porque conectei o código que escrevi. Existe o erro logo após

Erro Verilog (10170): Erro de formato HDL em seqdet.v (24) próximo ao texto do hub "if";

Esperando por um identificador ("se" é apenas uma palavra-chave de qualquer tipo de identificador alinhado), ou #, ou

de uma tarefa do curso, ou "(", com "{" ou um unário enorme operador,

current_state está associado a um registro de desenvolvimento e reset_state é inicializado em três 'b000 principais com declaração de parâmetro.

obrigado,

aravind

Esta instrução de caso não continha grandes instruções de abertura e fechamento

, e o dispositivo estava entre chaves, o que, na opinião excelente, era desnecessário. Não tenho certeza se estou exatamente. Mas agora não entendo todos os erros.

usado para bitstring. Use início e fim por outro lado.

Não se esqueça do "endcase".

usado para fazer bitstring. Em vez disso, use início e fim. Filme Não neste caso um "caso extremo".

Acelere seu PC hoje mesmo com este download fácil de usar.Error 10170 Verilog Hdl Syntax Error

Fehler 10170 Verilog Hdl Syntaxfehler

Fout 10170 Verilog Hdl Syntaxisfout

오류 10170 Verilog Hdl 구문 오류

Erreur 10170 Erreur De Syntaxe Verilog Hdl

Fel 10170 Verilog Hdl Syntaxfel

Errore 10170 Errore Di Sintassi Verilog Hdl

Blad 10170 Verilog Blad Skladni Hdl

Oshibka 10170 Sintaksicheskaya Oshibka Verilog Hdl

Error 10170 Error De Sintaxis De Verilog Hdl