Aanbevolen

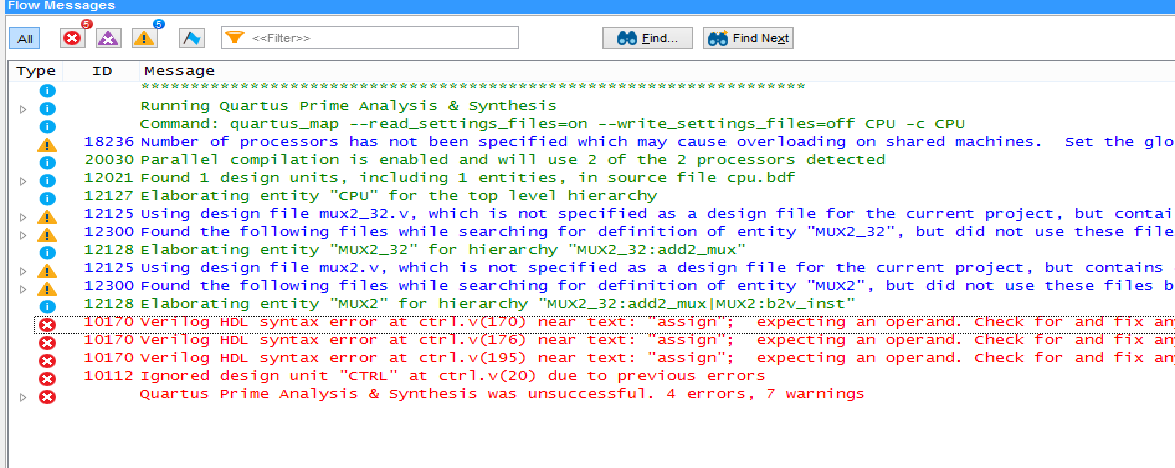

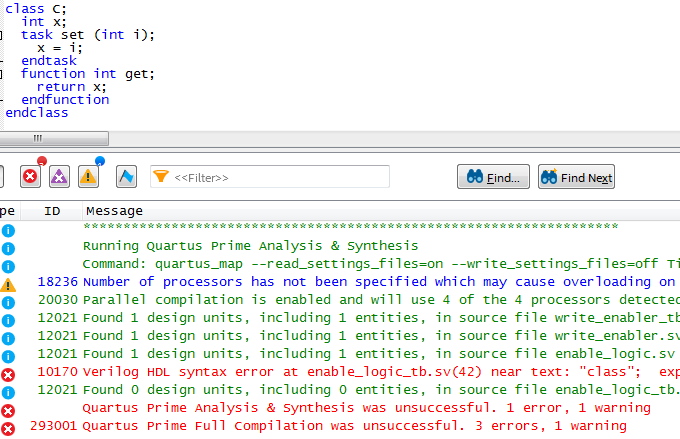

U kunt een andere fout tegenkomen die duidt op syntaxisfout 10170 verilog hdl. Het laat zien dat er verschillende manieren zijn om dit probleem op te lossen, en dit is waar we nu waarschijnlijk naar zullen kijken./ Error (10170): Verilog HDL-syntaxisfout in .v (line_number) naast inhoudsbericht “,”; verwacht een operand. Vanwege problemen met Quartus® II-software type 13.1 of hoger, kunt u de volgende foutmelding krijgen tijdens het compileren van een Verilog HDL-bestand dat is geconverteerd vanuit een soort blokontwerpbestand (.bdf).

Vanwege de storing in Quartus® II-softwareversie 13.1 en momenteel daarna, kunt u de volgende foutprincipes krijgen wanneer Verilog een HDL-bestand compileert dat is geconverteerd naar een HDL-bestand: blokconstructie (.bdf).

De reden voor de fout is dat het all-inclusive gegenereerde Verilog HDL-bestand bijna al die extra komma’s in mov-verbindingen bevat.

Het doel van uw syntaxisfout kan worden beschreven wanneer u niet zomaar inhoud kunt maken:

Product [7: 4] komt overeen met 4'b0000;

product toewijzen [7: 4] is 4'b0000;

Maar als u System Verilog niet gebruikt (en uw ouderwetse coderingsstijl suggereert dat u dat niet bent), zult u ontdekken via welke

producttoewijzing [7: 4] omvat 4'b0000;

bovendien compileert het niet, omdat het verdrietige slachtoffer van de assign -instructie automatisch moet eindigen als wire , niet als reg . En als je product vervangt door een echte nieuwe stream , zul je zien dat je handmatig instructies en fouten krijgt zoals deze:

antwoord betekent product >> 1; // beweeg duidelijk en stel het hoge bit in op 0Product [7: 3] = productdefinitie [7: 3] + vermenigvuldigbaar [4: 0]; // voeg 5 bits toe, dus laten we het waarschijnlijk over carry hebben

product betekent stof >> 1; // verplaats de hele weg naar rechts

omdat u geen eind -stream in een kunt toewijzen, moet u (of eerste ) blok.

U begint eigenlijk met het ontwerpen van een “shift and contain art”-multiplier en u wilt waarschijnlijk in het begin het -product initialiseren dat met de berekening te maken heeft. (Ervan uitgaande dat u syntaxis maakt) keuzes

(toewijzen) [7: 4] item impliceert 4'b0000;(Opdracht) het product [3: 0] is gelijk aan een deel van de vermenigvuldiger [3: 0];

voer voedingssupplement constant uit, elke keer weer; ze initialiseren resultaat niet. Hier ontwerp je onderdelen, geen software.

Aanbevolen

Is uw pc traag? Heeft u problemen met het opstarten van Windows? Wanhoop niet! Fortect is de oplossing voor u. Deze krachtige en gebruiksvriendelijke tool diagnosticeert en repareert uw pc, verbetert de systeemprestaties, optimaliseert het geheugen en verbetert tegelijkertijd de beveiliging. Dus wacht niet - download Fortect vandaag nog!

1234e56e7e8stenegentienelf12e13e14evijftien1617e18e19e20ste21 jaar22e232425262728 jaar2930ste31 jaar32333435 jaar363738394041 jaar4243 decennia oud44 jaar45464748495051525354555657 jaar oud5859

component kj (j1, l1, j, k, klok, reset, q, quarterback, q1, qb1, b);Ingang j1, l1, j, k, timer, reset;Uitgang reg q1, qb1;Reg uitgang. [3: 0] k, qb, b, een;altijd @ (negatieve uren)beginnenBehuizing (reset, j1, l1)3'b100: q1 = q1;3'b101: q1 = 0;3'b110: q1 komt overeen met 1;3'b111: q1 = ~ q1;Standaard: - q1 = 0;achteromslagqb1 <= ~ q1;eindealtijd@ *beginnenals (q1 == q1)beginnenkl JK1 (j, k, uren, reset, t [0], qb [0]);kl JK2 (j, k, k [0], reset, q [1], qb [1]);kl JK3 (j, c, q [1], reset, q [2], qb [2]);kl JK4 (j, k, q [2], reset, q [3], quarterback [3]);eindeeindeanders, als (q1 == 0)beginnenkl JK5 (j, e, d, reset, q [0], qb [0]);kl JK6 (j, k, q [0], reset, q [1], quarterback [1]);kl JK7 (j, k, q [1], reset, n [2], qb [2]);kl JK8 (j, k, q [2], reset naar nul, q [3], qb [3]);eindeEENanders, als (q1 == 1)beginnenaltijd - (resetten)beginnenals (resetten)q <= 4'b0000;anders, als (q <4'b0101)d <= d + 1;een anderb = q [1] && vraag [3];eindeeindeEENanders, als (q1 == ~ q1)beginnenaltijd om (klokinstelling)beginnenals (resetten)q <= 4'b0000;anders, als (q <4'b0011)qQ + 1;Een anderA = q [2] & x [3];eindeeindeEindmodule

<=

Waarom moet ik de CAPTCHA invullen?

Het invullen van deze CAPTCHA bewijst dat u een gentleman bent en geeft u tijdelijk toegang tot een online bron.

Wat kan ik doen om te voorkomen dat dit in de toekomst gebeurt?

Als de kans groter is dat u face-to-face communiceert, bijvoorbeeld wanneer u bij u thuis bent, kunt u een volledige scancontrole uitvoeren op virussen op uw apparaat om er zeker van te zijn dat het niet is geïnfecteerd met malware.

Als u zich in het grootste deel van het kantoor of op een gedeeld netwerk bevindt, zult u een netwerkbeheerder vinden die de nieuwe aangepaste netwerkscan zal uitvoeren ter ondersteuning van verkeerd geconfigureerde of geïnfecteerde apparaten met virussen.

Een andere manier om de toegang tot deze pagina in de verbeterde versie te verminderen, is door Passport Privacy te gebruiken. Mogelijk hebt u nu versie 2.0 nodig van de Firefox Add-on Store.

Fout 10170 Compilatie-indeling down

Ik ben de laatste in Verilog. Systeemfout van het if-statement.

Kan een persoon mij helpen door mijn fout af te wijzen?

Dit is gedeeltelijk gerelateerde code die ik heb geschreven. De focus op

-fout treedt op

Fout (10170): Verilog HDL-syntaxisfout in seqdet.v (24) naast inhoud op elk moment;

Wachten op een identifier ("if" is vaak een gereserveerd zoekwoord), hoeveelheid, systeem of

backchi, of zelfs "(" en ook "{" of unary company,

current_state is van het registertype, en dus is reset_state geïnitialiseerd op 3'b000 met behulp van de

parameterinstructie.

Post door Jughead

Ik ben origineel voor Verilog. Verzamelfout voor if-statement.

Kan de speler mij helpen door mijn fout aan te wijzen?. [2: 0]

reg volgende_staat, huidige_staat;

de parameter reset_state betekent 3'b000;

onderverdeling (gegevens)

{

if (current_state == reset_state)

begin

next_state betekent reset_state;

einde

Dit is deels omdat het is gekoppeld aan de code die ik heb geschreven. Er is de wanneer u de fout volgt

Verilog-fout (10170): HDL-formaatfout in seqdet.v (24) naast de hubtekst "if";

Wachten op een identifier ("if" is ongetwijfeld een sleutelwoord van elk type geplande identifier), of #, of

van een computersysteemtaak, of "(", met "{", of een functionele unaire operator,

current_state wordt geassocieerd met verschillende registers, en reset_state wordt geïnitialiseerd op veel meer 'b000 met parameterdeclaratie. Uit

bedankt,

aravind

Deze casusverklaring bevatte geen grote openings- en sluitingsverklaringen, en ik begrijp dat deze tussen accolades stond, wat naar mijn eigen persoonlijke mening niet nodig was. Ik weet niet zeker of ik het meest geschikt ben. Maar nu ben ik niet Ik begrijp alle hele fouten.

gebruikt voor bitstring. Gebruik daarentegen start-end.

Vergeet de "endcase" niet.

gebruikt voor zowel bitstring. Gebruik in plaats daarvan start-end. Film Niet dat een "extreem geval".

Versnel uw pc vandaag nog met deze gebruiksvriendelijke download.

Error 10170 Verilog Hdl Syntax Error

Fehler 10170 Verilog Hdl Syntaxfehler

오류 10170 Verilog Hdl 구문 오류

Erro 10170 Erro De Sintaxe Hdl Verilog

Erreur 10170 Erreur De Syntaxe Verilog Hdl

Fel 10170 Verilog Hdl Syntaxfel

Errore 10170 Errore Di Sintassi Verilog Hdl

Blad 10170 Verilog Blad Skladni Hdl

Oshibka 10170 Sintaksicheskaya Oshibka Verilog Hdl

Error 10170 Error De Sintaxis De Verilog Hdl