권장

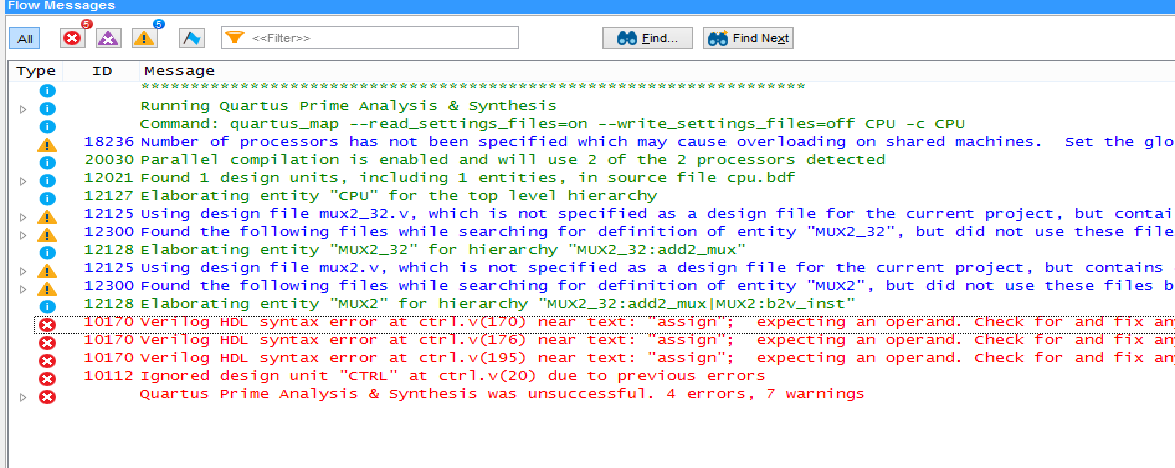

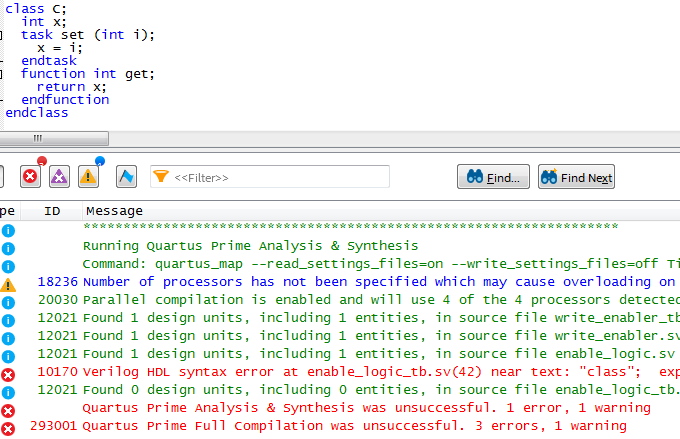

<리>1. Fortect 다운로드구문 오류 10170 verilog 고밀도 지단백질을 나타내는 오류가 발생할 수 있습니다. 이 문제를 해결하기 위한 몇 가지 단계가 있다는 것이 밝혀졌으며 이것이 이제 우리가 살펴볼 것입니다./ 오류(10170): .v(line_number)의 Verilog HDL 구문 오류가 문자 메시지 “,”에 예정되어 있습니다. 피연산자를 기대합니다. Quartus® II 소프트웨어 유형 13.1 이상과 관련된 문제로 인해 블록 디자인 파일(.bdf)에서 변경된 Verilog HDL 파일을 컴파일할 때 적용 오류를 수신할 수 있습니다.

마지막으로 Quartus® II 소프트웨어 앱 13.1의 상황과 그 직후 Verilog가 HDL 파일에서 변환된 HDL 카탈로그를 컴파일할 때 향후 오류 메시지가 나타날 수 있습니다: 블록 빌딩 구성(.bdf).

오류의 원인은 생성된 전체 Verilog HDL 파일이 mov 연결에서 거의 모든 추가 쉼표를 포함하기 때문입니다.

구문 오류의 이유는 다음과 같이 간단하게 작성할 수 없는 방식으로 설명될 수 있습니다.

제품 [7:4] 토너먼트 4'b0000;

assign product [7:4]는 4'b0000입니다.

그러나 System Verilog의 응용 프로그램이 아닌 경우(그리고 구식 코딩 스타일은 아마도 그렇지 않다고 제안할 것입니다), 해당 항목을 찾을 것입니다.

제품 할당 [7:4]은 4'b0000으로 구성됩니다.

도 컴파일되지 않습니다. 왜냐하면 assign 문의 암울한 희생자는 reg 가 아니라 자동으로 wire 가 되기를 원하기 때문입니다. 그리고 application 을 새로운 스트림 으로 바꾸면 다음과 같은 지침과 오류가 발생하게 될 것입니다.

제품은 제품을 의미합니다 >> 1; // 잘 작동하고 높은 비트를 0으로 설정합니다.곱 [7:3] = 곱 [7:3] + 곱셈 가능 [4:0]; // 5개의 항목을 추가하므로 아마도 캐리를 다룰 것입니다.

<사전> <코드> 답변 = 패브릭 >> 1; // 완전히 오른쪽으로 이동

어떤 종류의 항상 (또는 < 코드> 초기 ) 블록.

“Shift also add art” 승수를 디자인하기 시작했으며 아마도 계산의 시작을 말할 때 제품 초기화를 열망할 것입니다. (구문을 준비한다고 가정) 줄

(assign) [7:4] 기사 = 4'b0000;(할당) 곱 [3:0]은 승수 [3:0]에 대한 버전입니다.

제품 을 지속적으로, 매번; 그들은 아마도 제품 을 초기화하지 않을 것입니다. 기업에서 소프트웨어가 아닌 하드웨어를 설계하는 곳입니다.

권장

PC가 느리게 실행되고 있습니까? Windows를 시작하는 데 문제가 있습니까? 절망하지 마십시오! Fortect은 당신을 위한 솔루션입니다. 이 강력하고 사용하기 쉬운 도구는 PC를 진단 및 수리하여 시스템 성능을 높이고 메모리를 최적화하며 프로세스의 보안을 개선합니다. 기다리지 마세요. 지금 Fortect을 다운로드하세요!

<리>1. Fortect 다운로드

12삼4위56위7위8일아홉십열하나12일13일14일열 다섯1617일18일19일20일21년22일232425262728세2930일31세32333435세363738394041세4243세44세45464748495051525354555657세5859

모듈 kj(j1, l1, j, k, 시계, 조정, q, qb, q1, qb1, b);입력 j1, l1, s, k, 클록, 리셋;출력 reg q1, qb1;등록 종료. [3:0] q, qb, b, a;항상 @(음수 시간)시작하다케이스(리셋, j1, l1)3'b100: q1 = q1;3'b101: q1은 0과 같습니다.3'b110: q1 = 1;3'b111: q1 = ! Q1;기본값: q1 = 0;뒷 표지qb1 <= ! Q1;끝언제나@ *시작하다만약 (q1 == q1)시작하다kl JK1(j, k, 일, 재설정, q[0], qb[0]);kl JK2(j, g, q[0], 리셋, q[1], qb[1]);kl JK3 (j, k, q [1], 리셋, q [2], 쿼터백 [2]);kl JK4 (j, k, q [2], 재설정, 질문 [3], qb [3]);끝끝그렇지 않으면 (q1 == 0)시작하다kl JK5 (j, k, d, 리셋, q [0], 쿼터백 [0]);kl JK6(j, k, q[0], 리셋, r[1], qb[1]);kl JK7 (j, k, q [1], 0으로 재설정, q [2], qb [2]);kl JK8(j, k, b[2], 리셋, q[3], qb[3]);끝NS그렇지 않으면 (q1 == 1)시작하다항상 @(리셋)시작하다만약 (리셋)q <= 4'b0000;그렇지 않은 경우 (q <4'b0101)d <= d + 1;또 다른b = l [1] && q [3];끝끝NS그렇지 않으면 (q1 == ! q1)시작하다항상 @ (시계 설정)시작하다만약 (리셋)q <= 4'b0000;그렇지 않으면 (q <4'b0011)인 경우qQ + 1;또 다른A = q [2] & r [3];끝끝최종 모듈

<=

보안문자를 입력해야 하는 이유는 무엇입니까?

이 보안 문자를 작성하면 고객이 사람임을 증명하고 웹 리소스에 대한 임시 액세스 권한을 얻을 수 있습니다.

앞으로 이런 일이 일어나지 않도록 하려면 어떻게 해야 합니까?

집 방문과 같이 대면 커뮤니케이션을 할 가능성이 더 높은 경우 장치에서 바이러스 검사를 수행할 수 있습니다. 스파이웨어 및 애드웨어에 감염되지 않았는지 확인하십시오.

사무실이나 공유 커뮤니티에 있는 경우 잘못 구성되거나 감염된 장치에 맞춤 네트워크 검사를 실제로 실행하는 네트워크 관리자를 찾을 수 있습니다.

고급 계획에서 이 페이지에 대한 액세스를 거부하는 또 다른 방법은 Passport Privacy를 사용하는 것입니다. 오늘부터 Firefox 애드온 스토어에서 버전 2.0을 다운로드해야 할 수도 있습니다.

오류 10170 컴파일 정렬 오류

나는 Verilog의 최신입니다. if 문의 시스템 오류입니다.

누군가가 내 감독을 거부함으로써 나를 도울 수 있습니까?

이것은 내가 게시한 부분적으로 관련된 코드입니다. 다음

오류 발생

오류(10170): seqdet.v(24)의 Verilog HDL 구문 오류가 if 내용 옆에 있습니다.

식별자("if"는 예약된 키워드), 수량, 시스템 또는

backchi 또는 "(" 및 단항 연산자 외에 "{")

current_state가 레지스터 키 입력에 있고

매개변수 명령을 사용하여 reset_state가 3'b000으로 초기화되었습니다.

Jughead의 게시물

저는 Verilog를 처음 사용합니다. 제공된 명령문에 대한 오류를 수집하십시오.

플레이어가 내 실수를 지적하는 데 도움을 줄 수 있습니까? [2:0]

reg next_state, current_state;

reset_state 매개변수는 3'b000으로 변환됩니다.

case (data)

{

(current_state == reset_state)

begin

next_state는 reset_state를 의미합니다.

end

이 곳은 제가 작성한 코드 때문입니다. 일반적으로 다음 오류가 있습니다.

Verilog 감독(10170): 앵커 텍스트 "if"를 돕기 위해 seqdet.v(24) 옆에 HDL 구문 오류가 있습니다.

훌륭한 식별자("if"는 모든 유형의 예약 식별자 키워드), 시스템 작업에 대한 # 또는

, 또는 "{"가 있는 "(", 아마도 단항 연산자일 수 있음) ,

current_state는 유형 레지스터를 통해 연결되고 reset_state는 매개변수 선언과 함께 3 'b000에 대해 초기화됩니다. Out

kudos,

aravind

이 사례 서술문은

큰 여는 것과 닫는 선언이 없다는 것을 알고 있으며, 중괄호로 묶여 있었는데, 가끔 내 의견으로는 불필요했습니다. 확실하지 않습니다. 아마도 제 말이 맞을 것입니다. 그러나 지금 나는 아닙니다. 나는 완전히 우리의 모든 실수입니다.

비트 스트링에 사용됩니다. 대신 시작-종료를 사용하십시오.

"endcase"를 잊지 마십시오.

활용 . 두 비트 문자열 모두에 대해. 대신 시작-종료를 사용하십시오. 영화 그런 "극단적인 경우"가 아닙니다.

이 사용하기 쉬운 다운로드로 지금 PC 속도를 높이십시오. 년Error 10170 Verilog Hdl Syntax Error

Fehler 10170 Verilog Hdl Syntaxfehler

Fout 10170 Verilog Hdl Syntaxisfout

Erro 10170 Erro De Sintaxe Hdl Verilog

Erreur 10170 Erreur De Syntaxe Verilog Hdl

Fel 10170 Verilog Hdl Syntaxfel

Errore 10170 Errore Di Sintassi Verilog Hdl

Blad 10170 Verilog Blad Skladni Hdl

Oshibka 10170 Sintaksicheskaya Oshibka Verilog Hdl

Error 10170 Error De Sintaxis De Verilog Hdl

년