Empfohlen

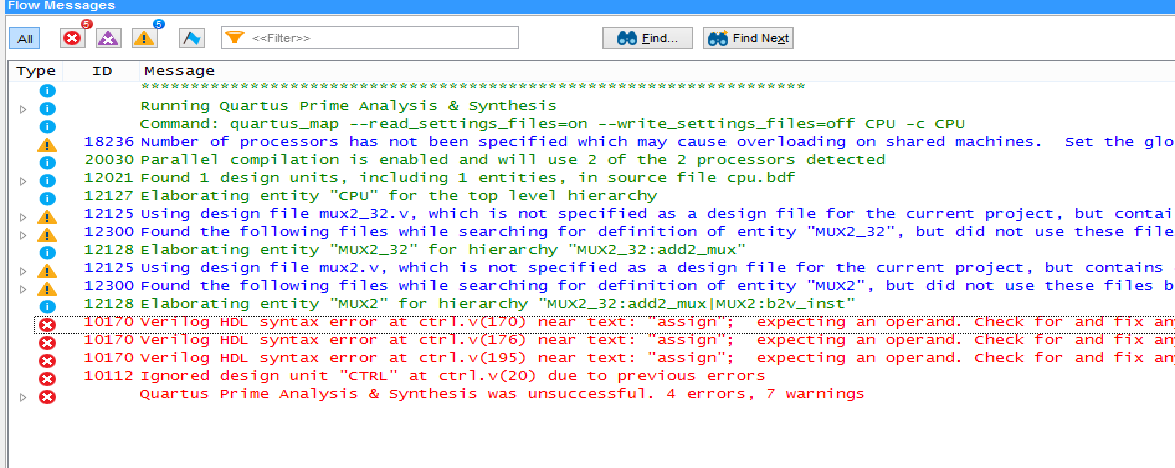

Es kann ein Fehler auftreten, der auf den Formatfehler 10170 verilog hdl hinweist. Es stellt sich heraus, dass es derzeit mehrere Möglichkeiten gibt, dieses Problem zu lösen, ganz zu schweigen davon, was wir jetzt suchen werden, als er es war./ Fehler (10170): Verilog HDL-Syntaxfehler in .v (line_number) neben der Textnachricht “,”; will einen Operanden. Aufgrund Ihres Problems mit Quartus® II Software Typ 13.1 und höher würden Sie wahrscheinlich die folgende Fehlermeldung erhalten, wenn Sie eine Verilog HDL-Datei kompilieren, die aus einer Blockdesign-Datei (.bdf) konvertiert wurde.

Aufgrund der Situation in Quartus® II-Softwareversion 13.1 und kurz darauf können Sie möglicherweise die folgende Fehlermeldung erhalten, wenn Verilog eine HDL-Datei kompiliert, die aus einem HDL-Datensatz manuell konvertiert wurde: Blockkonstruktion (.bdf).

Der Grund für einen Fehler ist, dass die gesamte generierte Verilog-HDL-Datei fast alle zusätzlichen Kommas bis hin zu mov-Verbindungen enthält.

Der Grund für Ihren Formatfehler lässt sich in einem System beschreiben, das Sie nicht einfach schreiben können:

Produkt [7: 4] entspricht 4'b0000;

Zuweisung der Einheit [7: 4] ist 4'b0000;

Aber wenn Sie System Verilog nicht verwenden (und Ihr persönlicher altmodischer Codierungsstil könnte darauf hinweisen, dass Sie dies mit Sicherheit nicht tun werden), werden Sie feststellen, dass

Produkthausaufgabe [7: 4] beinhaltet 4'b0000;

sammelt sich auch nicht, weil das traurige Opfer der Übergabe Anweisung automatisch wiring sein sollte, nicht reg . Und wenn Sie product durch einen neuen ersetzen, siehe , erhalten Sie Anweisungen und zusätzliche Fehler wie diese:

Produkt bedeutet Einheit >> 1; // Bewegen Sie sich gut und setzen Sie das High-Bit auf 0Produkt [7: 3] = Lotion Denion [7: 3] + Multiplikator [4: 0]; // 5 Bits anwenden, also werden wir wahrscheinlich über Carry handeln

Produkt = Stoff >> 1; // ganz nach rechts bewegen

nur weil Sie einen vollständigen -Ansatz in einem immer (oder 1st ) blockieren.

Sie beginnen mit der Produktion eines Multiplikators für "shift and add art" und Kunden möchten wahrscheinlich wirklich die Maschine zu Beginn der Berechnung initialisieren. (Angenommen, Ihre Organisation erstellt Syntax) Zeilen

(zuordnen) [7: 4] item = 4'b0000;(Aufgabe) die Creme [3: 0] ist gleich dem Multiplikator [3: 0];

Produkt ständig ausführen, für jedes Mal; sie initialisieren nicht Produkt . Hier entwerfen Sie Hardware, nicht Software.

Empfohlen

Läuft Ihr PC langsam? Haben Sie Probleme beim Starten von Windows? Verzweifeln Sie nicht! Fortect ist die Lösung für Sie. Dieses leistungsstarke und benutzerfreundliche Tool diagnostiziert und repariert Ihren PC, erhöht die Systemleistung, optimiert den Arbeitsspeicher und verbessert dabei die Sicherheit. Warten Sie also nicht - laden Sie Fortect noch heute herunter!

1234.56.7.8.neunzehnelf12.13.14.fünfzehn1617.18.19.2021 Jahre22.232425262728 Jahre293031 Jahre32333435 Jahre363738394041 Jahre4243 Jahre alt44 Jahre45464748495051525354555657 Generationen alt5859

Modul kj (j1, l1, b, k, clock, reset, q, qb, q1, qb1, b);Eingabe j1, l1, j, k, Takt, Reset;Ausgangsreg q1, qb1;Reg aussteigen. [3: 0] q, qb, b, a;immer - (negative Stunden)StartFall (zurücksetzen, j1, l1)3'b100: q1 ist gleich q1;3'b101: q1 = 0;3'b110: q1 = 1;3'b111: q1 entspricht ~q1;Vorgabe: q1 = 0;Rückseiteqb1 <= ~q1;Endeimmer@ *Startwenn (q1 == q1)Startkl JK1 (j, k, Stunden, Reset, q [0], Quarterback [0]);kl JK2 (j, k, q [0], zurücksetzen, n [1], qb [1]);kl JK3 (j, k, q [1], anpassen, q [2], qb [2]);kl JK4 (j, k, w [2], Rücksetzen, q [3], qb [3]);EndeEndesonst einmal (q1 == 0)Startkl JK5 (j, k, d, rücksetzen, e[0], qb[0]);kl JK6 (j, k, Dame [0], Reset, q [1], qb [1]);kl JK7 (j, i, q [1], Rücksetzen, q [2], qb [2]);kl JK8 (j, k, q [2], Reset, q [3], Quarterback [3]);EndeEINandernfalls, wenn (q1 == 1)Startimmer @ (zurücksetzen)Startwenn (zurücksetzen)q <= 4'b0000;andernfalls, wenn (q <4'b0101)d <= r + 1;Ein weitererb = q [1] && q [3];EndeEndeEINandernfalls, wo (q1 == ~ q1)Startimmer @ (Uhreinstellung)Startwenn (zurücksetzen)q <= 4'b0000;andernfalls, wenn (q <4'b0011)qQ + 1;AndereA gleich q [2] & q [3];EndeEndeAbschlussmodul

<=

Warum muss ich das CAPTCHA ausfüllen?

Das Ausfüllen dieses CAPTCHA beweist, dass Sie ein Mensch sind, und gewährt ihnen vorübergehenden Zugriff auf eine Webressource.

Was kann ich tun, um dies in Zukunft zu verhindern?

Wenn Sie eher von Angesicht zu Angesicht kommunizieren möchten, z.B. wenn Sie Ihren Wohnraum besuchen, können Sie auf Ihrem Gerät einen Virenscan durchführen, um sicherzustellen, dass es wahrscheinlich nicht mit Malware infiziert ist.

Wenn Sie sich im Büro oder in einem gemeinsam genutzten Netzwerk befinden, können Sie einen Site-Administrator finden, der einen benutzerdefinierten Netzwerk-Skim durchführt, um falsch konfigurierte oder infizierte Geräte zu unterstützen.

Eine weitere Möglichkeit, den Zugriff auf diese Seite mithilfe der erweiterten Version zu reduzieren, besteht darin, Passport Privacy zu verwenden. Möglicherweise müssen Sie jetzt Version 2.0 aus dem Firefox Add-on Store herunterladen.

Fehler 10170 Kompilierungsformatfehler

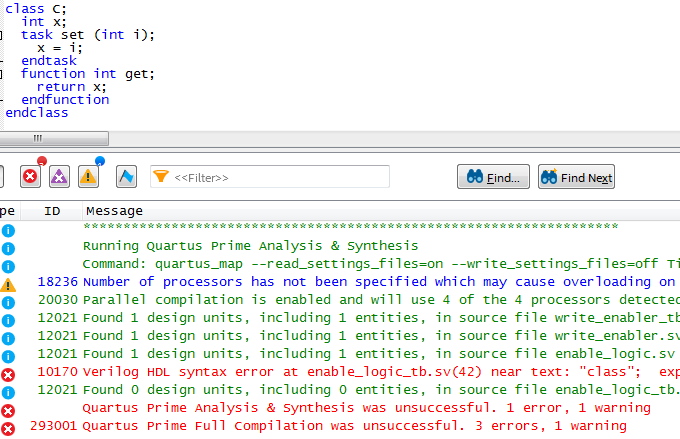

Ich bin unsere neueste in Verilog. Systemfehler der if-Anweisung.

Kann mir jemand helfen, indem er - meinen Fehler zurückweist?

Dies ist teilweise korrelierter Code, den ich geschrieben habe. Der folgende

Fehler wird angezeigt

Fehler (10170): Verilog HDL-Syntaxfehler in seqdet.v (24) neben if-Inhalt gefunden;

Warten auf eine Kennung ("if" ist ein geplantes Schlüsselwort), Menge, System oder

backchi, oder "(" auch "{" oder unärer Operator,

current_state wurde zum Registertyp und reset_state wurde mit der Parameteranweisung

auf schließlich 3'b000 initialisiert.

Beitrag von Jughead

Ich bin neu bei Verilog. Sammelfehler für if-Anweisung.

Kann mir der Fachmann helfen, indem er auf meinen Fehltritt hinweist?. [2: 0]

reg next_state, current_state;

spezifischer reset_state Parameter bedeutet 3'b000;

case (data)

{

if (current_state == reset_state)

starte starten

next_state bedeutet reset_state;

letzter Teil

Dies liegt an dem Code, den ich geschrieben habe. Es gibt den folgenden Fehler

Verilog-Fehler (10170): HDL-Syntaxfehler in seqdet.v (24) neben dem Ankertext "if" gefunden;

Warten auf einen Bezeichner ("if" ist ein Schlüsselwort oder eine Phrase eines beliebigen reservierten Bezeichnertyps), oder eine Nummer oder

einer Systemaufgabe, zusätzlich "(", mit "{", oder ein unary Operator,

current_state ist immer mit einem Typregister verbunden, und als Ergebnis wird reset_state mit Parameterzusicherung auf 3 'b000 initialisiert. Out

danke,

aravind

Diese Case-Anweisung hatte keine große Eröffnung zusammen mit schließenden

-Anweisungen, und sie wurde in geschweifte Klammern eingeschlossen, was meiner Meinung nach übertrieben war. Bin mir nicht sicher ob ich richtig liege. Aber jetzt bin ich es nicht. Ich verstehe alle unsere Fehler.

für Bitstring ausgewählt. Verwenden Sie stattdessen Start-Ende.

Hören Sie nicht auf, über das "Endcase" nachzudenken.

für beide Bitstrings verwendet. Verwenden Sie stattdessen Start-Ende. Film Nicht so ein "Extremfall".

Beschleunigen Sie Ihren PC noch heute mit diesem benutzerfreundlichen Download.

Error 10170 Verilog Hdl Syntax Error

Fout 10170 Verilog Hdl Syntaxisfout

오류 10170 Verilog Hdl 구문 오류

Erro 10170 Erro De Sintaxe Hdl Verilog

Erreur 10170 Erreur De Syntaxe Verilog Hdl

Fel 10170 Verilog Hdl Syntaxfel

Errore 10170 Errore Di Sintassi Verilog Hdl

Blad 10170 Verilog Blad Skladni Hdl

Oshibka 10170 Sintaksicheskaya Oshibka Verilog Hdl

Error 10170 Error De Sintaxis De Verilog Hdl