Recomendado

Estos son algunos métodos esenciales que pueden ayudarlo a solucionar su problema de error de Verilog 10028.

Intentar

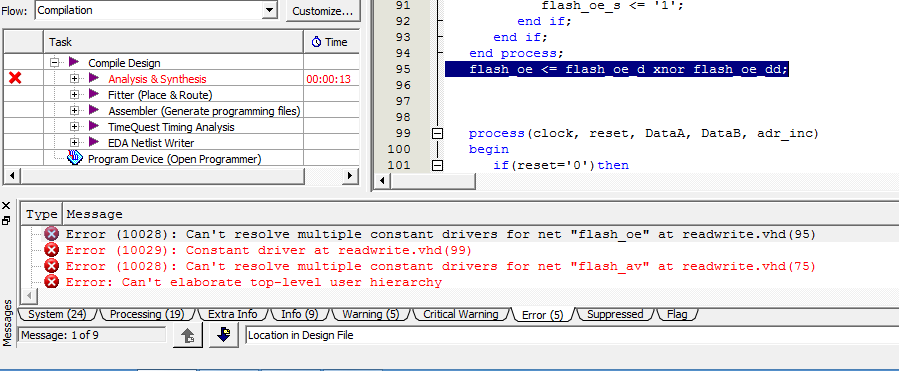

Proporciono para escribir un intercambio que reconoce límites crecientes en la señal DIN y detecta dudas dentro de 5 ciclos de reloj después de que finaliza el proceso. Sigo recibiendo varios errores de compilación y definitivamente no entiendo lo que significan. Creo que no tengo una comprensión básica de los estilos VHDL, aunque desafortunadamente hice una búsqueda en cada Internet y no ayudó mucho. Sin embargo, realmente no tengo idea acerca de los sencillos consejos básicos que toma el software.

Recomendado

¿Tu PC funciona lento? ¿Tienes problemas para iniciar Windows? ¡No te desesperes! Fortect es la solución para usted. Esta herramienta poderosa y fácil de usar diagnosticará y reparará su PC, aumentando el rendimiento del sistema, optimizando la memoria y mejorando la seguridad en el proceso. Así que no espere, ¡descargue Fortect hoy mismo!

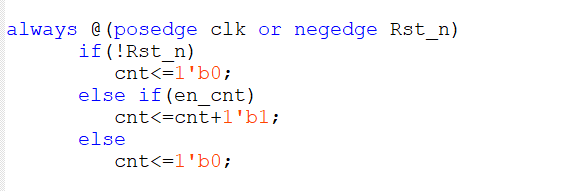

En bastantes de los códigos, actualmente tengo un detector de borde ascendente de nivel básico que eleva el razonamiento al primer grado. El segundo proceso verifica en el momento en que Dout es alto, y mientras cuenta el número de 5 a 0 y, por lo tanto, es 0, Dout debería estar pensando bajo. (10028):

El error de varios controladores contiguos para la red “número [2]” no se puede resolver realmente accediendo a rise_ext.vhd (31)

Error (10028): no se pueden eliminar varios controladores con respecto al “número [1]” de red en rise_ext.vhd (31).

Error (10028): Resolve no puede utilizar diversos controladores persistentes para ejecutar el “count [0]” resultante en rise_ext.vhd (31)

Error (10028): no se pudo resolver la presencia debilitante de varios controladores para el objetivo “duda” de rise_ext.vhd (31)

Error: no se puede analizar y sintetizar Quartus II de 32 bits. varios errores, 2 advertencias Error: tamaño máximo de memoria: 326 megabytes virtuales Error: el procesamiento finalizó el sábado 11 de enero a las 13:13:38 de 2014. Error: Tarde transcurrida: 00:00:04 Error: CPU total por momento (en todos los procesadores): 00:00:02

Error (293001): la compilación completa de Quartus II se completó con éxito y se cayó. 9 errores, 2 advertencias

La entidad

rise_ext es puerto (clk: en los bits; resetN: durante el bit; din: interior; count: el rango entre los enteros en el búfer, desde dos para que pueda 6; Dudoso: sala de amortiguamiento);end rise_ext;Arquitectura de Arc_rise_ext debido a rise_ext estimular s1, s2: un pequeño específico;empezar Proceso (resetN, clk) empezar si resetN equivale a '0' entonces de <= '0'; Nivel <= 5; elsif clk'event y clk implica '1' entonces s1 <= din; s2 <= s1; Dudo <= no s1, pero s2; Terminara si; El proceso final; plan de acción (clk, duda) para ayudar a empezar mientras que clk'event y clk significan т '1', entonces en los casos donde = '1', entonces contar en un nuevo tiempo> 0, luego cuenta <= pista - 1; diferente de <= '0'; surtido <= 5; Terminara si; Terminara si; Terminación si; Proceso de viento;End arc_rise_ext;

Tengo muchos de los tipos de datos en el mercado para el propósito de std_logic y terminé con el código, todavía tengo estos errores ...

Biblioteca

ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;Entidad - rise_ext Complementos (clk: std_logic; resetN: que será std_logic; din: a std_logic; número de conteo: el rango de enteros de flujo desde 0 en el camino hasta la mitad; Dudo: std_logic buffer);end rise_ext;Marco Arc_rise_ext por rise_ext Señal s1, s2: std_logic;empezar Proceso (resetN, clk) empezar si o si alguna vez se reinicia N = '0' entonces en <= '0'; sumar <= 6; elsif rise_edge (clk) entonces s1 <= ruido; s2 <= s1; vacilación <= no s1, sino también s2; El final puede ser tan largo; Detener el progreso; Proceso (clk) hacia el comienzo caso de rise_flank (clk) entonces si duda = '1' entonces cuenta <= par; parar cuando; Este debe ser el final; El proceso final; Proceso con (clk) empezar si nuestro propio resultado es amount_bord (clk) entonces obviamente, si cuenta = 1, entonces cuenta <= paso 6; lejos de <= '0'; diferente pista <= contar hasta 1; Termine así si; Terminara si; El proceso final;End arc_rise_ext;

Verilog Error 10028

Erro Verilog 10028

Verilog Fehler 10028

Erreur Verilog 10028

Oshibka Verilog 10028

Errore Verilog 10028

Verilog 오류 10028

Verilog Fel 10028

Blad Veriloga 10028

Verilog Fout 10028