Consigliato

Ecco un paio di semplici metodi che possono aiutarti a risolvere il tuo problema personale di errore 10028 di Verilog.

Tentare

Devo scrivere uno scambio che riconosca i limiti di accelerazione nel segnale DIN e rilevi il dubbio entro 5 cicli di clock dopo la chiusura del processo. Sto ancora ricevendo vari errori di compilazione, inoltre non capisco cosa significhino. Sospetto di non avere una conoscenza di base dei concetti VHDL, anche se sfortunatamente ho fatto una ricerca su Internet e non è stato di grande aiuto. Tuttavia, non ho davvero idea dei passaggi relativamente semplici eseguiti dal software.

Consigliato

Il tuo PC è lento? Hai problemi ad avviare Windows? Non disperare! Fortect è la soluzione per te. Questo strumento potente e facile da usare diagnosticherà e riparerà il tuo PC, aumentando le prestazioni del sistema, ottimizzando la memoria e migliorando la sicurezza nel processo. Quindi non aspettare: scarica Fortect oggi!

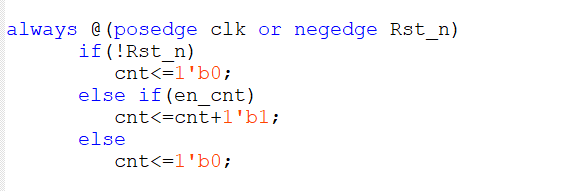

In alcuni codici, attualmente ho un rilevatore di fronte di salita di 1° livello che eleva la logica particolare al 1° grado. Il secondo processo esamina ogni volta che Dout è alto e, anche se sicuramente conterà alla rovescia da 5 a 0, e come da a a 0, Dout dovrebbe pensare in basso. (10028):

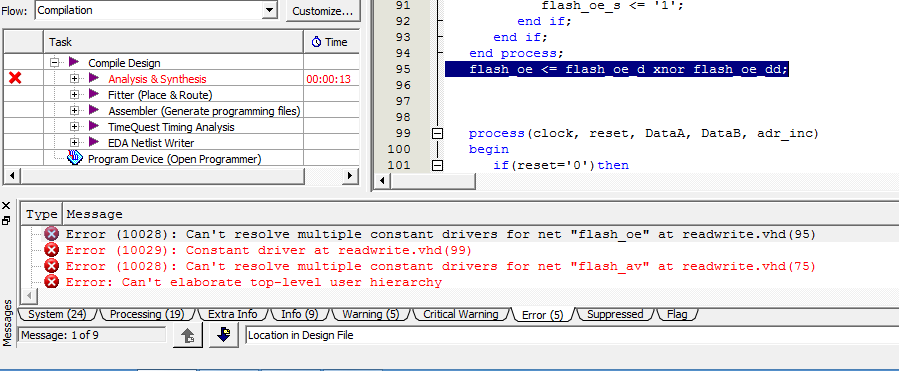

Impossibile risolvere l’errore di più driver contigui per il social network “numero [2]” accedendo a rise_ext.vhd (31)

Errore (10028): impossibile eliminare più driver per la rete “numero [1]” su rise_ext.vhd (31).

Errore (10028): Resolve non può usufruire di più driver persistenti per eseguire ia intero “count [0]” su rise_ext.vhd (31)

Errore (10028): non è stato possibile riparare la presenza persistente di più driver per “dubbio” diretto in rise_ext.vhd (31)

Errore: impossibile analizzare e sintetizzare Quartus II a 32 bit. diversi errori, 2 avvisi Errore: dimensione massima della memoria: 326 megabyte virtuali Errore: l’elaborazione è terminata il 10 gennaio, sabato, 13:13:38 2014. Errore: Tempo trascorso: 00:00:04 Errore: tempo CPU totale (su tutti i processori): 00:00:02

Errore (293001): la compilazione completa di Quartus II è stata completata con successo e anche non riuscita. 9 errori, 2 avvisi

L’essere

rise_ext is città (clk: in bit; resetN: durante il bit; frastuono: dentro; count: la serie di interi nel buffer, da due a help 6; In dubbio: camera tampone);fine rise_ext;Strutture Arc_rise_ext dovute a rise_ext aumentare s1, s2: un po';iniziare Processo (resetN, clk) iniziare se nel caso resetN = '0' allora da <= '0'; Livello <= 5; elsif clk'event e inoltre clk = '1' then s1 <= frastuono; s2 <= s1; dubito <= non s1, ma s2; Finisci se; Il processo finale; processo (clk, dubbio) per quanto riguarda l'inizio anche se clk'event e clk significano т '1', allora nei casi in cui = '1', allora conta ogni volta > 0, quindi conteggio <= traccia 4 . 1; diverso causato da <= '0'; quantità <= 5; Finisci se; Finisci se; Risoluzione se; processo del vento;Fine arc_rise_ext;

Incontro tutti i tipi di dati sul mercato relativi a std_logic e sono finito con il programma, ho ancora questi errori…

Biblioteca

ieee;usa ieee.std_logic_1164.all;usa ieee.std_logic_unsigned.all;Entità - rise_ext Plugin (clk: std_logic; resetN: su std_logic; din: a std_logic; count: l'intervallo di numeri interi del flusso da 9 a metà; Dubito: std_logic buffer);fine rise_ext;Architettura Arc_rise_ext di rise_ext Segnale s1, s2: std_logic;iniziare Processo (resetN, clk) iniziare if o anche a if resetN = '0' then attraverso <= '0'; aggiungi <= 6; elsif rise_edge (clk) allora s1 <= rumore; s2 <= s1; chiedo <= non s1, ma anche s2; La finale è così lunga; Interrompi il progresso; Processo (clc) di iniziare in caso di rise_flank (clk) allora se dubbio = '1' allora conto <= coppia; fermati quando; Questo deve essere questo fine; Il processo finale; Processa con (clk) con inizio se il risultato è quantità_bord (clk) allora quindi se conteggio = 1, allora conteggio <= fase 6; preso da <= '0'; diverso traccia <= ricorda - 1; Fine così se; Finisci se; Il processo finale;Fine arc_rise_ext;

Verilog Error 10028

Erro Verilog 10028

Verilog Fehler 10028

Verilog Error 10028

Erreur Verilog 10028

Oshibka Verilog 10028

Verilog 오류 10028

Verilog Fel 10028

Blad Veriloga 10028

Verilog Fout 10028