Recommandé

Voici quelques méthodes simples qui peuvent vous aider à gérer votre problème d’erreur Verilog 10028.

Tenter

Je dois rédiger un échange qui distingue les limites croissantes du signal DIN et identifie le doute dans les 5 cycles d’horloge suivant la fin de l’expérience. Je reçois toujours diverses complications de compilation et je ne comprends pas ce qu’elles signifient. Je pense que je n’ai pas une compréhension de base des concepts VHDL, même si malheureusement j’ai fait un moteur de recherche sur Internet et cela n’a pas beaucoup aidé. Cependant, je n’ai vraiment aucune idée des étapes de base d’une personne prises par le logiciel.

Recommandé

Votre PC est-il lent ? Avez-vous des problèmes pour démarrer Windows ? Ne désespérez pas ! Fortect est la solution pour vous. Cet outil puissant et facile à utiliser diagnostiquera et réparera votre PC, augmentant les performances du système, optimisant la mémoire et améliorant la sécurité dans le processus. Alors n'attendez pas - téléchargez Fortect dès aujourd'hui !

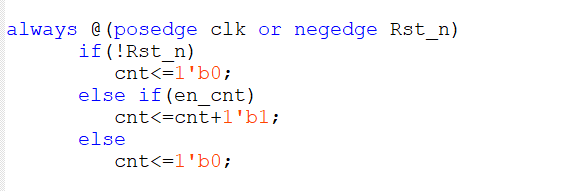

Dans certains des codes, j’ai actuellement certainement un détecteur de front montant de 1er niveau qui monte la logique au 1er niveau. La deuxième étape vérifie chaque fois que Dout est élevé, et tandis que le programme compte à rebours de 5 à 0, et donc jusqu’à 0, Dout devrait penser plus petit. (10028) :

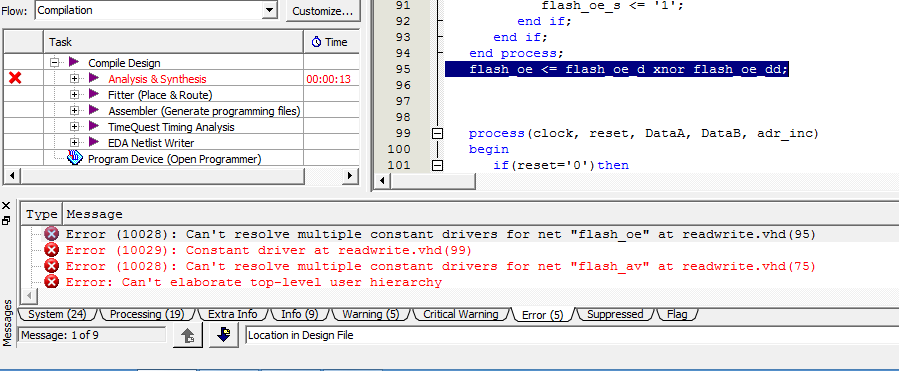

L’erreur de plusieurs pilotes contigus pour le réseau social “numéro [2]” ne peut pas être résolue en accédant à rise_ext.vhd (31)

Erreur (10028) : Impossible d’éliminer les pilotes du réseau « numéro [1] » sur rise_ext.vhd (31).

Erreur (10028): Résoudre n’est certainement pas utiliser plusieurs pilotes persistants pour exécuter le site Web “count [0]” sur rise_ext.vhd (31)

Erreur (10028) : la présence persistante de plusieurs pilotes pour le « doute » ciblé dans rise_ext.vhd (31) n’a pas pu être terminée

Erreur : impossible d’analyser et de synthétiser Quartus II 32 bits. plusieurs erreurs, 2 avertissements Erreur : Taille maximale de la mémoire : 326 types de mégaoctets électroniques Erreur : Le traitement s’est terminé le 11 janvier, samedi, 13:13:38 2014. Erreur : Temps écoulé : 00:00:04 Erreur : Temps CPU total (sur tous les processeurs) : 00:00:02

Erreur (293001) : La compilation complète de Quartus II s’est terminée confortablement et a échoué. 9 erreurs, 2 avertissements

L’état

rise_ext est port (clk : en bits ; resetN : à partir du cours du bit ; vacarme : à l'intérieur ; count : souvent la plage d'entiers dans le tampon, d'une paire de à 6 ; Douteux : chambre tampon) ;fin rise_ext;Arc_rise_ext structures dues à rise_ext fortifier s1, s2 : un peu ;pour commencer Processus (resetN, clk) pouvoir commencer évidemment si resetN = '0' alors via <= '0'; Niveau <= 5 ; elsif clk'event et par conséquent clk = '1' alors s1 <= din ; s2 <= s1 ; Je doute <= pas s1, mais s2 ; Fin si; Le processus final ; processus (clk, doute) si tu veux commencer bien que clk'event et clk signifient т '1', alors dans les cas où signifie '1', alors compter avec n'importe quel temps> 0, puis compte <= garder une trace de - 1 ; différent y compris <= '0' ; quantité <= 5 ; Fin si; Fin si; Résiliation si ; Processus du vent ;Fin arc_rise_ext ;

J'ai tous les types de données sur le présent pour std_logic et je me suis retrouvé avec le code réel, j'ai toujours ces erreurs...

Bibliothèque

ieee;utilisez ieee.std_logic_1164.all ;utilisez ieee.std_logic_unsigned.all ;Entité - rise_ext Plugins (clk : std_logic ; resetN : qui peut std_logic ; din : vers std_logic ; count : la plage d'entiers de flux allant de 0 à la moitié ; Je doute : std_logic buffer) ;fin rise_ext;Architecture Arc_rise_ext par rise_ext Signal s1, s2 : std_logic ;pour commencer Processus (resetN, clk) pour être sûr de commencer dans le cas où ou si resetN = '0' alors à l'origine de <= '0'; ajouter <= 6 ; elsif rise_edge (clk) alors s1 <= bruit ; s2 <= s1 ; doute <= pas s1, mais en plus s2; La fin est si longue ; Arrêter le progrès ; Processus (clk) pour commencer en cas de rise_flank (clk) alors si doute = '1' alors compte <= paire ; arrêter quand; Ce doit être une fin particulière ; Le processus final ; Traiteravec (clk) être commencer et si le résultat estmount_bord (clk) alors si compte = 1, alors compte <= décision 6 ; loin de <= '0'; différent piste <= compter - 1 ; Fin ainsi , si; Fin si; Le processus final ;Fin arc_rise_ext ;

Verilog Error 10028

Erro Verilog 10028

Verilog Fehler 10028

Verilog Error 10028

Oshibka Verilog 10028

Errore Verilog 10028

Verilog 오류 10028

Verilog Fel 10028

Blad Veriloga 10028

Verilog Fout 10028