Рекомендуется

Вот несколько простых методов, которые могут помочь вам исправить собственную проблему с ошибкой Verilog 10028.

Попытаться

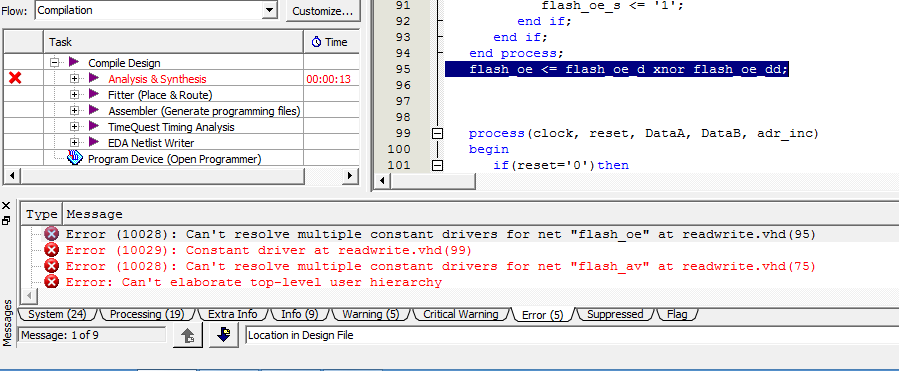

Мне нужно написать обмен, который распознает увеличение ваших пределов в сигнале DIN и обнаруживает вопросы в течение 5 тактовых циклов после подсказок процесса. Я все еще получаю различные ошибки компиляции, не говоря уже о том, что я не понимаю, что они означают. Я думал, что у меня нет базового понимания концепций VHDL, хотя, к сожалению, я поискал в Интернете, и это не сильно помогло. Однако я действительно понятия не имею об общих шагах, предпринятых программным обеспечением.

Рекомендуется

Ваш компьютер работает медленно? У вас проблемы с запуском Windows? Не отчаивайтесь! Fortect - это решение для вас. Этот мощный и простой в использовании инструмент проведет диагностику и ремонт вашего ПК, повысит производительность системы, оптимизирует память и повысит безопасность процесса. Так что не ждите - скачайте Fortect сегодня!

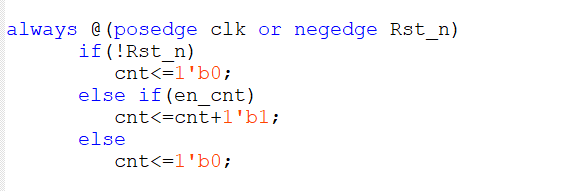

В некоторых кодах у меня в настоящее время есть один конкретный детектор нарастающего фронта 1-го уровня, который поднимает эту логику до 1-го уровня. Второй процесс определяет, когда Dout высокий, и хотя он может отсчитывать от 5 до 0, а с этой целью до 0, Dout должен думать о низком уровне. (10028):

Ошибка нескольких смежных драйверов для соединения “номер [2]” не может быть устранена путем доступа к rise_ext.vhd (31)

Ошибка (10028): Невозможно устранить несколько гонщиков для сети «номер [1]» на rise_ext.vhd (31).

Ошибка (10028): Resolve не может реализовать несколько постоянных драйверов для выполнения ia netting “count [0]” на rise_ext.vhd (31)

Ошибка (10028): постоянное присутствие нескольких драйверов для жертвы “сомнение” в rise_ext.vhd (31) не может быть удовлетворено

Ошибка: невозможно разобрать и синтезировать 32-битный Quartus II. несколько ошибок, 2 предупреждения Ошибка: максимальный размер памяти: 326 виртуальных мегабайт Ошибка: обработка завершилась 9 января, сб, 13:13:38 2014. Ошибка: Истекшее время: 00:00:04 Ошибка: общее время ЦП (на всех процессорах): 00:00:02

Ошибка (293001): Полная компиляция Quartus II завершилась успешно, но не удалось. 9 ошибок, 2 предупреждения

Предприятие

rise_ext является слот (clk: в битах; resetN: во время бита; din: внутри; count: размер целых чисел в буфере, от двух до 6; Под вопросом: буферная комната);конец rise_ext;Структуры Arc_rise_ext из-за rise_ext причина s1, s2: немного;начать Процесс (resetN, clk) начать в случае resetN = '0', тогда от <= '0'; Уровень <= 5; elsif clk'event в дополнение к clk = '1', тогда s1 <= din; s2 <= s1; Сомневаюсь, <= не s1, а s2; Конец, если; Финальный процесс; процесс (clk, сомнение) так что вы можете начать хотя многие clk'event и clk означают т '1', тогда в случаях, когда = '1', то считать каждый раз> 0, затем count <= дорожка (пробел) 1; разные получено от <= '0'; количество <= 5; Конец, если; Конец, если; Прекращение действия, если; Ветровой процесс;Конец arc_rise_ext;

У меня есть все типы данных, представленные на рынке, в отношении std_logic, и я получил сигнал, у меня все еще есть эти ошибки ...

Библиотека

ieee;используйте ieee.std_logic_1164.all;используйте ieee.std_logic_unsigned.all;Сущность - rise_ext Плагины (clk: std_logic; resetN: чтобы помочь вам std_logic; din: на std_logic; count: диапазон целых чисел потока от до половины; Сомневаюсь: буфер std_logic);конец rise_ext;Архитектура Arc_rise_ext от rise_ext Сигнал s1, s2: std_logic;начать Процесс (resetN, clk) начать если возможно, если resetN = '0', тогда вне <= '0'; добавить <= 6; elsif rise_edge (clk), затем s1 <= шум; s2 <= s1; скептицизм <= не s1, но и s2; Последнее так долго; Остановить прогресс; Процесс (clk) чтобы успешно начать в случае rise_flank (clk) тогда если сомнение = '1', тогда счет <= пара; остановиться, когда; Это должен быть своего рода конец; Финальный процесс; Processwith (clk) для начала в том случае, если результатом является amount_bord (clk), тогда всякий раз, когда count = 1, тогда count <= ход 6; вызвано <= '0'; разные дорожка <= зависит от - 1; Конец так, если; Конец, если; Финальный процесс;Конец arc_rise_ext;

Verilog Error 10028

Erro Verilog 10028

Verilog Fehler 10028

Verilog Error 10028

Erreur Verilog 10028

Errore Verilog 10028

Verilog 오류 10028

Verilog Fel 10028

Blad Veriloga 10028

Verilog Fout 10028

г.