Rekommenderas

Här är några enkla metoder som bör hjälpa dig att fixa ditt Verilog error 10028-problem.

Att försöka

Jag måste skriva ett bra utbyte som känner igen ökande gränser i DIN-signalen och upptäcker tvivel inom 5 klockperioder efter att processen avslutats. Jag flyttar fortfarande på olika kompileringsfel och förstår inte vad de betyder. Jag tror att jag inte har en speciell grundläggande förståelse för VHDL-koncept, även om jag tyvärr gjorde en sökning på internet och detta hjälpte inte mycket. Men jag har verkligen en idé om de grundläggande stegen som tas av hela programvaran.

Rekommenderas

Körs din dator långsamt? Har du problem med att starta Windows? Misströsta inte! Fortect är lösningen för dig. Detta kraftfulla och lättanvända verktyg kommer att diagnostisera och reparera din dator, öka systemets prestanda, optimera minnet och förbättra säkerheten i processen. Så vänta inte - ladda ner Fortect idag!

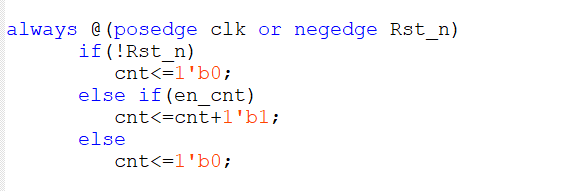

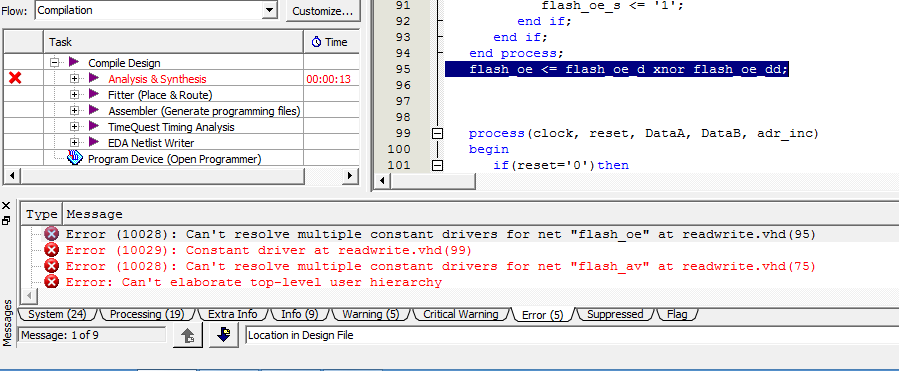

I några av skrivningarna har jag för närvarande en 1:a nivå stigande bankdetektor som höjer logiken till 1:a nivå. Den andra processen kontrollerar när Dout höjs, och medan den räknar ner från enkel till 0, och därför till 0, måste Dout tänka lågt. (10028):

Fel flera kontinuerliga drivrutiner för nätverket “nummer [2]” kan inte åtgärdas genom att gå till rise_ext.vhd (31)

Fel (10028): Det går inte att eliminera flera drivrutiner för nätverket “nummer [1]” när rise_ext.vhd (31).

Fel (10028): Resolve kan inte använda flera beständiga drivrutiner för att exekvera bl.a. netto “count [0]” på rise_ext.vhd (31)

Fel (10028): ihållande närvaro av en eller flera drivrutiner för målet “tvivel” i rise_ext.vhd (31) kunde lätt inte lösas

Fel: Det går inte att analysera och syntetisera 32-bitars Quartus II. flera fel, bara två varningar Fel: Maximal minnesskala: 326 virtuella megabyte Fel: Bearbetningen avslutades den 11 januari, lör, 13:13:38 2014. Fel: Förfluten tid: 00:00:04 Fel: Total CPU-tid (över nästan processorer): 00:00:02

Fel (293001): Fullständig kompilering av Quartus II slutfördes framgångsrikt och misslyckades. 9 fel, ett par varningar

Entiteten

rise_ext är port (clk: i bitar; resetN: under bit; din: inuti; count: intervallet av heltal i hela bufferten, från två till 6; Tveksamt: buffertrum);slut rise_ext;Arc_rise_ext-arkitektur på grund av rise_ext stimulera s1, s2: lite;att börja Process (återställN, clk) att börja om resetN = '0' då från <= '0'; Nivå <= 5; elsif clk'event och clk = '1' då s1 <= din; s2 <= sl; Jag tvivlar <= faktiskt inte s1, utan s2; Sluta om; Den sista processen; process (clk, tvivel) att börja även om clk'event och även clk betyder т '1', alltså i bärväskor där = '1', alltså räkna när som helst > 0, då överväga <= spår - 1; annorlunda från <= '0'; kvantitet <= 5; Sluta om; Sluta om; Uppsägning om; Vindprocess;End arc_rise_ext;

Jag har alla typer av data på marknaden för std_logic och jag avslutade med koden, jag har fortfarande något av dessa fel ...

Bibliotek

ieee;använd ieee.std_logic_1164.all;använd ieee.std_logic_unsigned.all;Entity lectronic rise_ext Plugins (clk: std_logic; återställN: till std_logic; brus: till std_logic; count: intervallet som involverar strömheltal från 0 till hälften; Jag tvivlar: std_logic buffer);slut rise_ext;Arc_rise_ext arkitektur i princip rise_ext Signal s1, s2: std_logic;att börja Process (återställN, clk) att börja om eller om resetN är lika med '0' då från <= '0'; lägg till <= 6; elsif rise_edge (clk) då s1 <= brus; s2 <= sl; tvivla <= inte nödvändigtvis s1, utan också s2; Slutet är så långt; Stoppa framsteg; Process (clk) att börja vid mest rise_flank (clk) då om tvivel betyder '1' då betala för <= par; avvärja när; Detta måste vara slutet; Den sista processen; Processwith (clk) att börja om resultatet har blivit mängd_bord (clk) då om räkna = bara en viss, alltså kvantifiera <= steg 6; från <= '0'; annorlunda mäta <= antal - 1; Sluta så om; Sluta om; Den sista processen;End arc_rise_ext;

Verilog Error 10028

Erro Verilog 10028

Verilog Fehler 10028

Verilog Error 10028

Erreur Verilog 10028

Oshibka Verilog 10028

Errore Verilog 10028

Verilog 오류 10028

Blad Veriloga 10028

Verilog Fout 10028