Recommended

Here are some simple methods that can help you fix your Verilog error 10028 problem.

To attempt

I have to write an exchange that recognizes increasing limits in the DIN signal and detects doubt within 5 clock cycles after the process ends. I am still getting various compilation errors and do not understand what they mean. I think I don’t have a basic understanding of VHDL concepts, although unfortunately I did a search on the internet and it didn’t help much. However, I really have no idea about the basic steps taken by the software.

Recommended

Is your PC running slow? Do you have problems starting up Windows? Don't despair! Fortect is the solution for you. This powerful and easy-to-use tool will diagnose and repair your PC, increasing system performance, optimizing memory, and improving security in the process. So don't wait - download Fortect today!

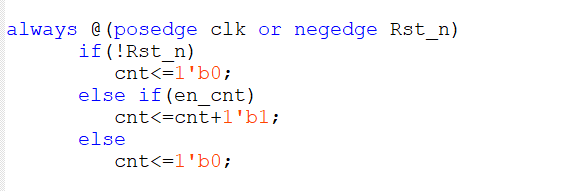

In some of the codes, I currently have a 1st level rising edge detector which raises the logic to 1st grade. The second process checks whenever Dout is high, and while it does count down from 5 to 0, and therefore to 0, Dout should be thinking low. (10028):

Error multiple contiguous drivers for network “number [2]” cannot be resolved by accessing rise_ext.vhd (31)

Error (10028): Unable to eliminate multiple drivers for network “number [1]” on rise_ext.vhd (31).

Error (10028): Resolve cannot use multiple persistent drivers to execute ia net “count [0]” on rise_ext.vhd (31)

Error (10028): persistent presence of multiple drivers for target “doubt” in rise_ext.vhd (31) could not be resolved

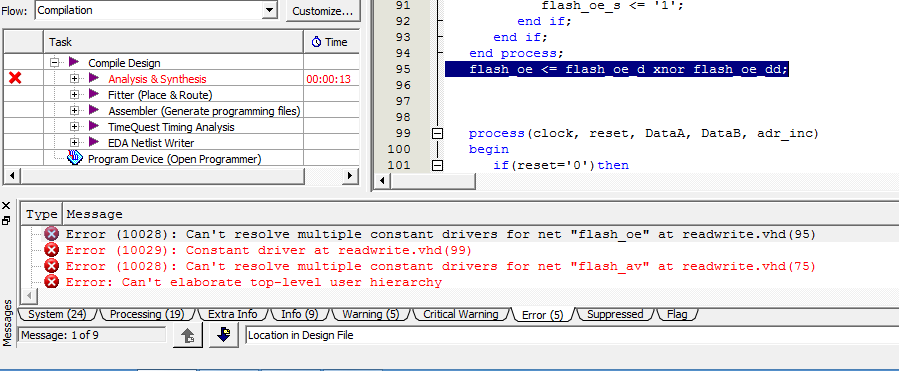

Error: Unable to parse and synthesize 32-bit Quartus II. several errors, 2 warnings Error: Maximum memory size: 326 virtual megabytes Error: Processing ended on Jan 11, Sat, 13:13:38 2014. Error: Elapsed time: 00:00:04 Error: Total CPU time (across all processors): 00:00:02

Error (293001): Full compilation of Quartus II completed successfully and failed. 9 errors, 2 warnings

The entity

rise_ext is port (clk: in bits; resetN: during bit; din: inside; count: the range of integers in the buffer, from two to 6; Doubtful: buffer room);end rise_ext;Arc_rise_ext architecture due to rise_ext stimulate s1, s2: a little;to begin Process (resetN, clk) to begin if resetN = '0' then from <= '0'; Level <= 5; elsif clk'event and clk = '1' then s1 <= din; s2 <= s1; I doubt <= not s1, but s2; End if; The final process; process (clk, doubt) to begin although clk'event and clk mean т '1', then in cases where = '1', then count at any time> 0, then count <= track - 1; different from <= '0'; quantity <= 5; End if; End if; Termination if; Wind process;End arc_rise_ext;

I have all the data types on the market for std_logic and I ended up with the code, I still have these errors ...

Library

ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;Entity - rise_ext Plugins (clk: std_logic; resetN: to std_logic; din: to std_logic; count: the range of stream integers from 0 to half; I doubt: std_logic buffer);end rise_ext;Arc_rise_ext architecture by rise_ext Signal s1, s2: std_logic;to begin Process (resetN, clk) to begin if or if resetN = '0' then from <= '0'; add <= 6; elsif rise_edge (clk) then s1 <= noise; s2 <= s1; doubt <= not s1, but also s2; The end is so long; Stop progress; Process (clk) to begin in case of rise_flank (clk) then if doubt = '1' then account <= pair; stop when; This must be the end; The final process; Processwith (clk) to begin if the result is amount_bord (clk) then if count = 1, then count <= step 6; from <= '0'; different track <= count - 1; End so if; End if; The final process;End arc_rise_ext;

Erro Verilog 10028

Verilog Fehler 10028

Verilog Error 10028

Erreur Verilog 10028

Oshibka Verilog 10028

Errore Verilog 10028

Verilog 오류 10028

Verilog Fel 10028

Blad Veriloga 10028

Verilog Fout 10028