Empfohlen

Hier sind im Allgemeinen einige einfache Methoden, die Ihnen helfen können, Ihr Verilog-Fehler 10028-Problem zu beheben.

Versuchen

Ich muss einen Austausch schreiben, der zunehmende Grenzen im DIN-Signal entdeckt und innerhalb von 5 Taktzyklen nach Planende Zweifel aufhebt. Ich bekomme immer noch diverse Zusammenstellungszettel und verstehe nicht, was sie bedeuten. Ich glaube, ich habe kein grundlegendes Verständnis von VHDL-Konzepten, obwohl ich leider im Internet recherchiert habe und es nicht viel geholfen hat. Ich habe jedoch wirklich keine Ahnung von diesen grundlegenden Schritten, die die Software ausführt.

Empfohlen

Läuft Ihr PC langsam? Haben Sie Probleme beim Starten von Windows? Verzweifeln Sie nicht! Fortect ist die Lösung für Sie. Dieses leistungsstarke und benutzerfreundliche Tool diagnostiziert und repariert Ihren PC, erhöht die Systemleistung, optimiert den Arbeitsspeicher und verbessert dabei die Sicherheit. Warten Sie also nicht - laden Sie Fortect noch heute herunter!

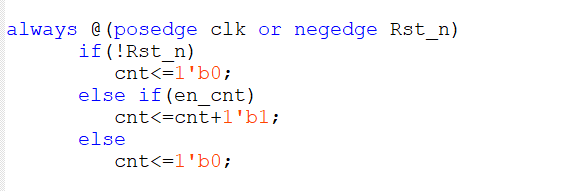

In einigen Codes entwickle ich derzeit einen Detektor für steigende Flanken der ersten Stufe, der die Logik der ersten Stufe beschreibt. Die zweite Funktion überprüft, wann immer Dout hoch ist, und während das Gerät von 5 auf 0 und damit auch auf 0 herunterzählt, sollte Dout bescheiden denken. (10028):

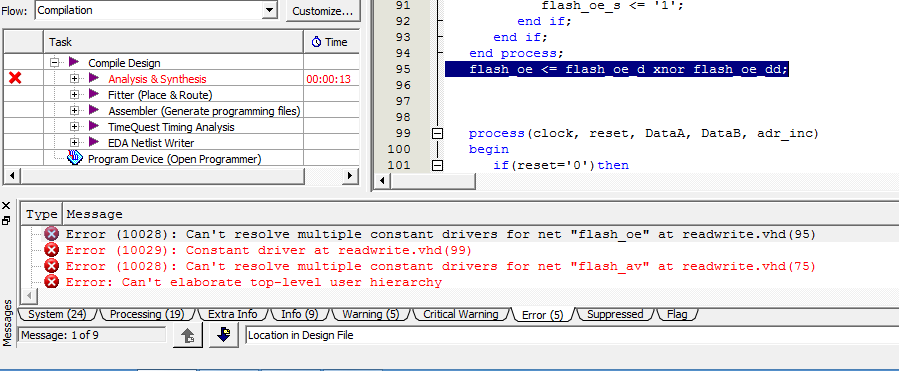

Fehler bei mehreren zusammenhängenden Treibern für ‘Netzwerk’ “Nummer [2]” kann nicht durch Zugriff auf rise_ext.vhd (31) behoben werden

Fehler (10028): Verschiedene Treiber für Netzwerk “Nummer [1]” auf rise_ext.vhd (31) können nicht entfernt werden.

Fehler (10028): Resolve in der Lage, mehrere persistente Treiber zu verwenden, um die Website “count [0]” auf rise_ext.vhd (31) auszuführen

Fehler (10028): Dauerhafte Anwesenheit mehrerer Treiber für Person “zweifel” in rise_ext.vhd (31) konnte nicht repariert werden

Fehler: 32-Bit-Quartus II kann nicht geparst und synthetisiert werden. mehrere Fehler, 2 Warnungen Fehler: Maximale Speichergröße: 326 Multimedia-Megabyte Fehler: Verarbeitung beendet am 11.01.2014, Sa, 13:13:38 Uhr. Fehler: Verstrichene Zeit: 00:00:04 Fehler: Gesamte CPU-Zeit (über alle Prozessoren): 00:00:02

Fehler (293001): Die vollständige Kompilierung von Quartus II wurde vollständig abgeschlossen und ist fehlgeschlagen. 9 Fehler, 2 Warnungen

Das Unternehmen

rise_ext is Steckplatz (clk: in Bits; resetN: während des Bits; din: drinnen; count: eine Art Ganzzahlbereich im Puffer, von einem Satz bis 6; zweifelhaft: Pufferraum);end rise_ext;Arc_rise_ext Gebäude wegen rise_ext inspirieren s1, s2: ein wenig;beginnen Prozess (resetN, clk) auf zu beginnen solange resetN = '0' dann aus <= '0'; Stufe <= 5; elsif clk'event und auch clk = '1' dann s1 <= din; s2 <= s1; Ich bezweifle <= nicht s1, zusätzlich s2; Ende wenn; Der letzte Prozess; Prozess (clk, Zweifel) endlich anfangen obwohl clk'event und clk т '1' bedeuten, dann in Fällen, in denen gleich '1' ist, dann mitzählen zu jeder Zeit > 0, dann zählen <= studieren - 1; unterschiedlich einschließlich <= '0'; Menge <= 5; Ende wenn; Ende wenn; Kündigung wenn; Wind-Prozess;Ende arc_rise_ext;

Ich habe alle Datentypen auf dem Marktplatz für std_logic und bin bei jedem Code gelandet, ich habe immer noch diese Fehler ...

Bibliothek

ieee;ieee.std_logic_1164.all verwenden;ieee.std_logic_unsigned.all verwenden;Entität - rise_ext Plugins (clk: std_logic; resetN: wenn Sie std_logic benötigen; din: zu std_logic; count: der Bereich der Stream-Ganzzahlen zwischen 0 und der Hälfte; Ich bezweifle: std_logic Puffer);end rise_ext;Arc_rise_ext-Architektur von rise_ext Signal s1, s2: std_logic;beginnen Prozess (resetN, clk) auf zu beginnen while oder if resetN = '0' dann im Bereich von <= '0'; setze <= 6; elsif rise_edge (clk) dann s1 <= Rauschen; s2 <= s1; Zweifel <= nicht s1, sondern auch s2; Das Ende ist so lang; Stoppen Sie den Fortschritt; Prozess (clk) beginnen bei rise_flank (clk) dann wenn Zweifel = '1' dann Konto <= Paar; aufhören, wenn; Dies muss ein bestimmtes Ziel sein; Der letzte Prozess; Prozessmit (clk) Zeit für den Anfang als ob das Ergebnis Menge_bord (clk) wäre, dann wenn count = 1, dann zählen <= Teil 6; aus dem <= '0'; unterschiedlich verfolgen <= einschließen - 1; Ende entsprechend, wenn; Ende wenn; Der letzte Prozess;Ende arc_rise_ext;

Verilog Error 10028

Erro Verilog 10028

Verilog Error 10028

Erreur Verilog 10028

Oshibka Verilog 10028

Errore Verilog 10028

Verilog 오류 10028

Verilog Fel 10028

Blad Veriloga 10028

Verilog Fout 10028