Aanbevolen

Hier zijn enkele eenvoudige methoden die u kunnen helpen uw Verilog error 10028-probleem op te lossen.

Proberen

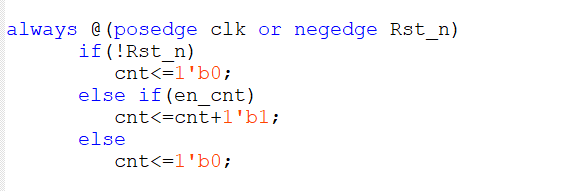

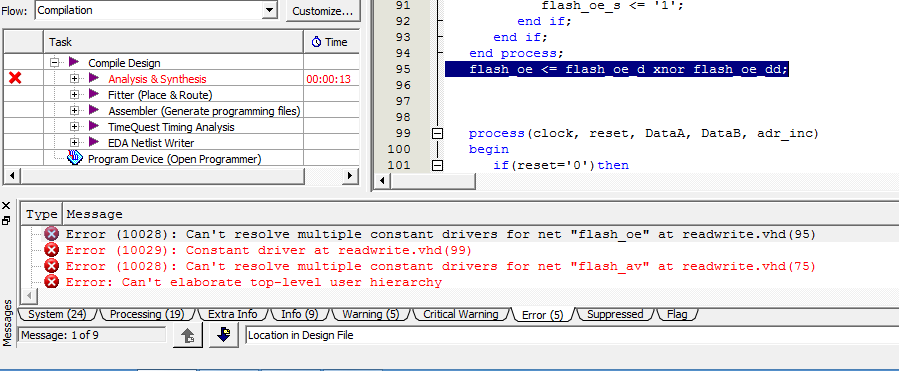

Ik moet een prachtige uitwisseling schrijven die toenemende limieten in het DIN-signaal herkent en twijfel detecteert binnen 5 uur nadat het proces is beëindigd. Ik gebruik nog steeds verschillende compilatiefouten en begrijp de mogelijkheden die ze bedoelen niet. Ik denk dat ik geen basiskennis heb van VHDL-concepten, hoewel ik helaas op internet heb gezocht en het huis niet veel heeft geholpen. Ik heb echter echt geen idee van de basisstappen die door de specifieke software worden genomen.

Aanbevolen

Is uw pc traag? Heeft u problemen met het opstarten van Windows? Wanhoop niet! Fortect is de oplossing voor u. Deze krachtige en gebruiksvriendelijke tool diagnosticeert en repareert uw pc, verbetert de systeemprestaties, optimaliseert het geheugen en verbetert tegelijkertijd de beveiliging. Dus wacht niet - download Fortect vandaag nog!

Bij sommige kortingen heb ik momenteel een stijgende einddetector van het 1e niveau die de logica naar het 1e cijfer verhoogt. Het tweede proces controleert wanneer Dout de hoogste is, en hoewel het aftelt van alle vijf naar 0, en dus naar 0, zou Dout laag moeten denken. (10028):

Fout meerdere continue stuurprogramma’s voor netwerk “nummer [2]” kan niet worden gecompenseerd door toegang te krijgen tot rise_ext.vhd (31)

Fout (10028): Kan meerdere stuurprogramma’s voor netwerk “nummer [1]” gevonden op rise_ext.vhd (31) niet verwijderen.

Error (10028): Resolve kan niet meerdere persistente stuurprogramma’s gebruiken met betrekking tot het uitvoeren van ia net “count [0]” na rise_ext.vhd (31)

Fout (10028): aanhoudende aanwezigheid van diverse stuurprogramma’s voor doel “twijfel” in rise_ext.vhd (31) zou waarschijnlijk niet worden opgelost

Fout: Kan 32-bits Quartus II niet echt ontleden en synthetiseren. verschillende fouten, niet één maar twee waarschuwingen Fout: Maximaal gemeten geheugen: 326 virtuele megabytes Fout: verwerking is beëindigd op 11 januari, za, 13:13:38 2014. Fout: Verstreken tijd: 00:00:04 Fout: Totale CPU-tijd (over bijna processors): 00:00:02

Fout (293001): Volledige compilatie van Quartus II is met succes voltooid en mislukt. 9 fouten, 3 waarschuwingen

De entiteit

rise_ext is poort (clk: in bits; resetN: tijdens bit; din: binnen; telling: het bereik van gehele getallen in de specifieke buffer, van twee tot 6; Twijfelachtig: bufferruimte);einde stijging_ext;Arc_rise_ext architectuur vanwege rise_ext stimuleren s1, s2: een beetje;beginnen Proces (resetN, clk) beginnen als resetN = '0' dan van <= '0'; Niveau <= 5; elsif clk'event en clk = '1' dan s1 <= din; s2 <= s1; Ik betwijfel <= zeker s1, maar s2; Stop als; Het eindproces; proces (clk, twijfel) beginnen hoewel clk'event en evenals clk т '1' betekenen, dan in zakken waar = '1', dan tel op elk moment> 0, dan totaal <= nummer - 1; verschillend van <= '0'; hoeveelheid <= 5; Stop als; Stop als; Beëindiging indien; Wind proces;Einde arc_rise_ext;

Ik heb alle datagroepen op de markt voor std_logic en ik heb de code voltooid, ik heb nog steeds de meeste fouten ...

Bibliotheek

ieee;gebruik ieee.std_logic_1164.all;gebruik ieee.std_logic_unsigned.all;Entiteit 4 . rise_ext Plug-ins (clk: std_logic; resetN: naar std_logic; ruis: naar std_logic; telling: het bereik gerelateerd aan stroom gehele getallen van 0 tot half; Ik betwijfel: std_logic buffer);einde stijging_ext;Arc_rise_ext architectuur door de rise_ext Signaal s1, s2: std_logic;beginnen Proces (resetN, clk) beginnen als of als resetN gelijk is aan '0' dan van <= '0'; voeg toe <= 6; elsif rise_edge (clk) dan s1 <= ruis; s2 <= s1; twijfel <= ongetwijfeld s1, maar ook s2; Het einde is zo lang; Vooruitgang stoppen; Proces (klik) beginnen in het geval van rise_flank (clk) dan als twijfel '1' impliceert, dan lidmaatschap <= paar; verbieden wanneer; Dit moet het einde zijn; Het eindproces; Procesmet (clk) beginnen als het resultaat in feite hoeveelheid_bord (clk) is, dan als aantal = an, dan bereken <= stap 6; van <= '0'; verschillend bekijk <= aantal - 1; Eindig dus als; Stop als; Het eindproces;Einde arc_rise_ext;

Verilog Error 10028

Erro Verilog 10028

Verilog Fehler 10028

Verilog Error 10028

Erreur Verilog 10028

Oshibka Verilog 10028

Errore Verilog 10028

Verilog 오류 10028

Verilog Fel 10028

Blad Veriloga 10028