Zalecane

Oto kilka prostych metod, które mogą pomóc w rozwiązaniu problemu z błędną kalkulacją Verilog 10028.

Próbować

Muszę stworzyć wymianę, która rozpoznaje rosnące limity w ogólnym sygnale DIN i wykrywa wątpliwości w ciągu 5 cykli zegara po zakończeniu procesu. Otrzymuję teraz różne błędy kompilacji i nie do końca rozumiem, co one oznaczają. Myślę, że nie rozwijam podstawowego zrozumienia pojęć VHDL, chociaż niestety przeszukałem internet i niewiele to pomogło. Jednak tak naprawdę nie mam pojęcia o podstawowych krokach podejmowanych z oprogramowania.

Zalecane

Czy Twój komputer działa wolno? Masz problemy z uruchomieniem systemu Windows? Nie rozpaczaj! Fortect to rozwiązanie dla Ciebie. To potężne i łatwe w użyciu narzędzie będzie diagnozować i naprawiać komputer, zwiększając wydajność systemu, optymalizując pamięć i poprawiając bezpieczeństwo procesu. Więc nie czekaj — pobierz Fortect już dziś!

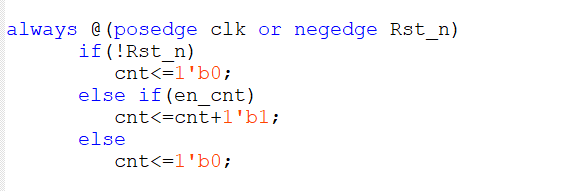

W niektórych typowych kodach, obecnie mam nadchodzący detektor krawędzi pierwszego poziomu, który podnosi logikę do 13 stopnia. Drugi proces sprawdza, gdy Dout często jest wysoki i chociaż odlicza od 5 do 0, a więc do 0, Dout powinien myśleć nisko. (10028):

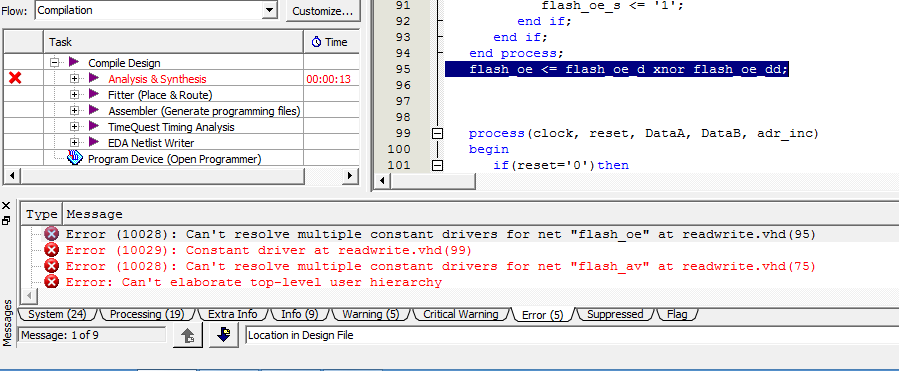

Błąd różnych sąsiadujących sterowników sieci „numer [2]” nie może być całkowicie rozwiązany przez dostęp do rise_ext.vhd (31)

Błąd (10028): Nie można wyeliminować wielu sterowników dla organizacji „numer [1]” w rise_ext.vhd (31).

Błąd (10028): Resolve nie może użyć wielu stałych pracowników dostarczających do wykonania ia net “count [0]” związanego z rise_ext.vhd (31)

Błąd (10028): uporczywa obecność najczęściej powiązana z wieloma sterownikami dla docelowych „wątpliwości” w rise_ext.vhd (31) z pewnością nie może zostać rozwiązana

Błąd: Nie można przeanalizować i zsyntetyzować 32-bitowego Quartus II. kilka wpadek, 2 ostrzeżenia Błąd: maksymalna zdolność do zapamiętania rozmiaru: 326 wirtualnych megabajtów Błąd: przetwarzanie zakończyło się 11 stycznia, sobota, 13:13:38 2014. Błąd: Czas, który upłynął: 00:00:04 Błąd: Całkowity czas procesora (tylko procesory): 00:00:02

Błąd (293001): Pełna kompilacja utworzona przez Quartus II zakończyła się pomyślnie i nie powiodła się. 9 poślizgów, 2 ostrzeżenia

Jednostka

rise_ext is port (clk: w bitach; resetN: podczas bitu; din: wewnątrz; count: zakres liczb całkowitych w buforze, od dwóch do 6; Wątpliwe: pomieszczenie buforowe);koniec wzrost_ex;Architektura Arc_rise_ext ze względu na wzrost_ext stymulować s1, s2: absolutnie mało;zacząć Proces (resetN, clk) zacząć jeśli zresetujN = '0' wtedy od <= '0'; Poziom <= 5; elsif clk'event i clk = '1' wtedy s1 <= din; s2 <= s1; ja zwątpienie <= nie s1, ale s2; Koniec jeśli; Ostateczny proces; skrót (clk, wątpliwość) zacząć chociaż clk'event jeszcze clk oznacza т '1', to tutaj w przypadkach, gdzie = '1', wtedy liczyć w dowolnym momencie> 0, to być zależnym <= ścieżka - 1; inny; różny od <= '0'; ilość <= 5; Koniec jeśli; Koniec jeśli; Wypowiedzenie, jeżeli; proces wiatru;Zakończ arc_rise_ext;

Mam wszystkie typy rekordów na rynku dla std_logic i skończyłem z kodem, nadal mam te błędy ...

Biblioteka

ieee;użyj ieee.std_logic_1164.all;użyj ieee.std_logic_unsigned.all;Jednostka - wzrost_ext Wtyczki (clk: std_logic; resetN: do std_logic; din: do std_logic; count: zakres do końca liczb całkowitych strumienia od 0 do połowy; Wątpię: bufor std_logic);koniec wzrost_ex;Architektura Arc_rise_ext za rise_ext Sygnał s1, s2: std_logic;zacząć Proces (resetN, clk) zacząć jeśli lub jeśli resetN jest równe '0' wtedy od <= '0'; dodaj <= 6; elsif rise_edge (clk) to s1 <= hałas; s2 <= s1; wątpić <= i nigdy s1, ale także s2; Koniec jest taki, że tak długo; Zatrzymaj postęp; Proces (clk) zacząć w dylemacie wzrostu_flank (clk) wtedy jeśli sceptycyzm = '1' wtedy konto <= para; odejść, kiedy; To musi być koniec; Ostateczny proces; Przetwarzaj z (clk) zacząć jeśli wynikiem będzie prawdopodobnie kwota_bord (clk) to jeśli liczba implikuje 1, to liczba <= krok 6; od <= '0'; inny; różny ścieżka <= liczba - 1; Koniec więc jeśli; Koniec jeśli; Ostateczny proces;Zakończ arc_rise_ext;

Verilog Error 10028

Erro Verilog 10028

Verilog Fehler 10028

Verilog Error 10028

Erreur Verilog 10028

Oshibka Verilog 10028

Errore Verilog 10028

Verilog 오류 10028

Verilog Fel 10028

Verilog Fout 10028